Figure 50. dma interrupt request generation – Zilog Z80180 User Manual

Page 129

Z8018x

Family MPU User Manual

114

UM005003-0703

DMAC Internal Interrupts

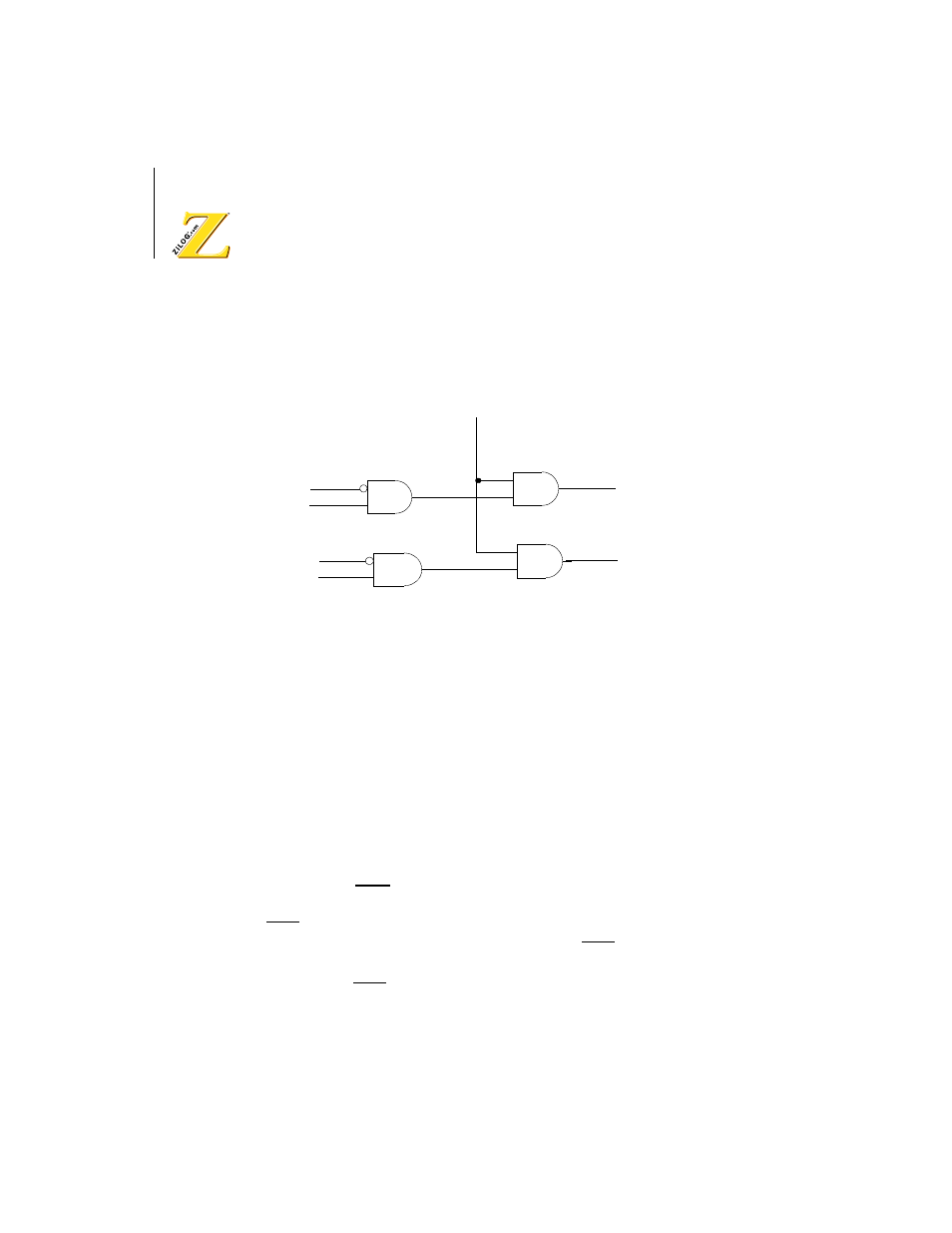

Figure 50 illustrates the internal DMA interrupt request generation circuit.

Figure 50. DMA Interrupt Request Generation

DE0 and DE1 are automatically cleared to

0

by the Z8X180 at the

completion (byte count is

0

) of a DMA operation for channel 0 and

channel 1, respectively. They remain

0

until a

1

is written. Because DE0:

and DE1 use level sense, an interrupt occurs if the CPU IEF1 flag is set to

1

. Therefore, the DMA termination interrupt service routine disables

further DMA interrupts (by programming the channel DIE bit is

0

) before

enabling CPU interrupts (for example, IEF1 is set to

1

). After reloading

the DMAC address and count registers, the DIE bit can be set to

1

to

reenable the channel interrupt, and at the same time DMA can resume by

programming the channel DE bit =

1

.

DMAC and NMI

NMI, unlike all other interrupts, automatically disables DMAC operation

by clearing the DME bit of DSTAT. Thus, the NMI interrupt service

routine responds to time-critical events without delay due to DMAC bus

usage. Also, NMI can be effectively used as an external DMA abort input,

recognizing that both channels are suspended by the clearing of DME.

DE1

DIE1

DE0

DIE0

IEF1

DMA ch1 Interrupt

Request

DMA ch0 Interrupt

Request