Figure 21. sleep timing diagram – Zilog Z80180 User Manual

Page 50

Z8018x

Family MPU User Manual

UM005003-0703

35

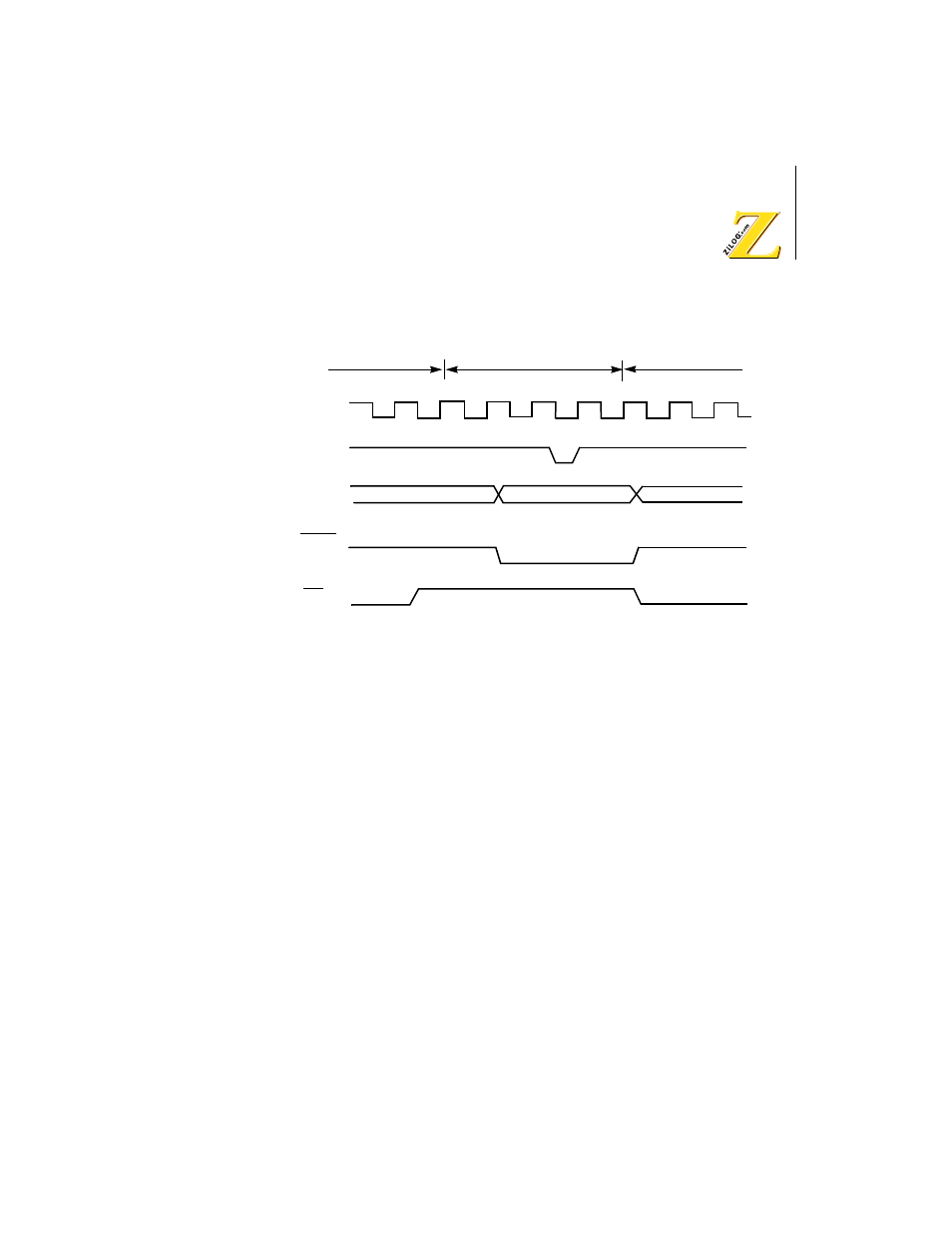

Figure 21. SLEEP Timing Diagram

IOSTOP Mode

IOSTOP mode is entered by setting the IOSTOP bit of the I/O Control

Register (ICR) to

1

. In this case, on-chip I/O (ASCI, CSI/O, PRT) stops

operating. However, the CPU continues to operate. Recovery from

IOSTOP mode is by resetting the IOSTOP bit in ICR to

0

.

SYSTEM STOP Mode

SYSTEM STOP mode is the combination of SLEEP and IOSTOP modes.

SYSTEM STOP mode is entered by setting the IOSTOP bit in ICR to

1

followed by execution of the SLP instruction. In this mode, on-chip I/O

and CPU stop operating, reducing power consumption. Recovery from

SYSTEM STOP mode is the same as recovery from SLEEP mode, noting

that internal I/O sources, (disabled by IOSTOP) cannot generate a

recovery interrupt.

T2

M1

Phi

A0

–

A19

HALT

T1

T2

TS

TS

T1

T2

T3

INT1, NMI

SLP 2nd Op Code

SLEEP mode

Op Code Fetch or Interrupt

Acknowledge Cycle

Fetch Cycle

SLP 2nd Op Code address

FFFFFH

T3