Timer control register (tcr) – Zilog Z80180 User Manual

Page 176

Z8018x

Family MPU User Manual

UM005003-0703

161

Timer Control Register (TCR)

TCR monitors both channels (PRT0, PRT1) TMDR status. It also controls

enabling and disabling of down counting and interrupts along with

controlling output pin A18/TOUT for PRT1.

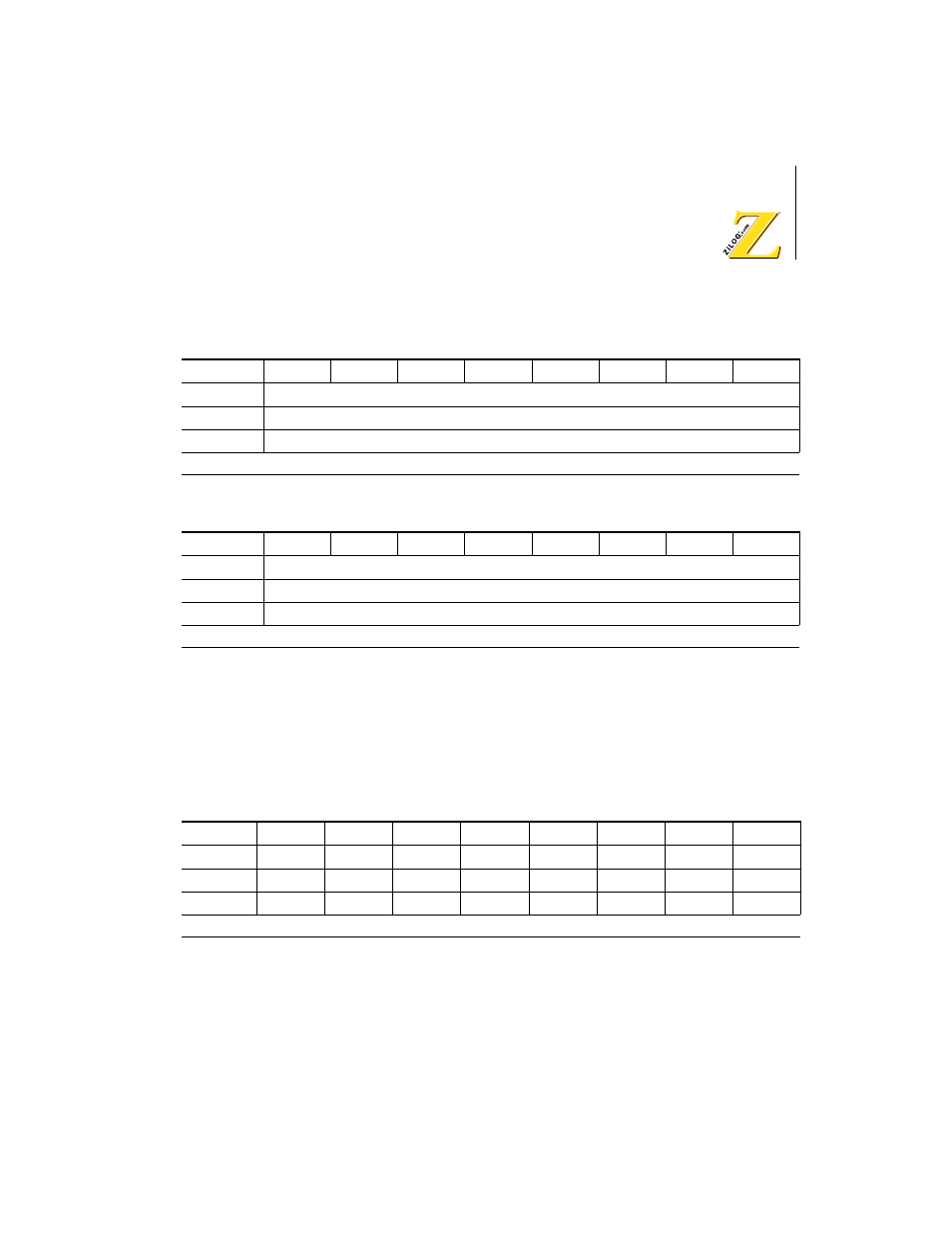

Timer Reload Register Channel 1L (RLDR1L: 16H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

Timer Reload Data

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Timer Reload Register Channel 1H (RLDR1H: 17H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

Timer Reload Data

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Timer Control Register (TCR: 10H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

TIF1

TIF0

TIE1

TIE0

TOC1

TOC0

TDE1

TDE0

R/W

R

R

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable