Table 6, I/o address map for z80180-class processors only – Zilog Z80180 User Manual

Page 59

Z8018x

Family MPU User Manual

44

UM005003-0703

address to

0

. These instructions are IN0, OUT0, OTIM, OTIMR, OTDM,

OTDMR and TSTIO (see Instruction Set).

When writing to an internal I/O register, the same I/O write occurs on the

external bus. However, the duplicate external I/O write cycle exhibits

internal I/O write cycle timing. For example, the WAIT input and

programmable Wait State generator are ignored. Similarly, internal I/O

read cycles also cause a duplicate external I/O read cycle. However, the

external read data is ignored by the Z8X180.

Normally, external I/O addresses should be chosen to avoid overlap with

internal I/O addresses and duplicate I/O accesses.

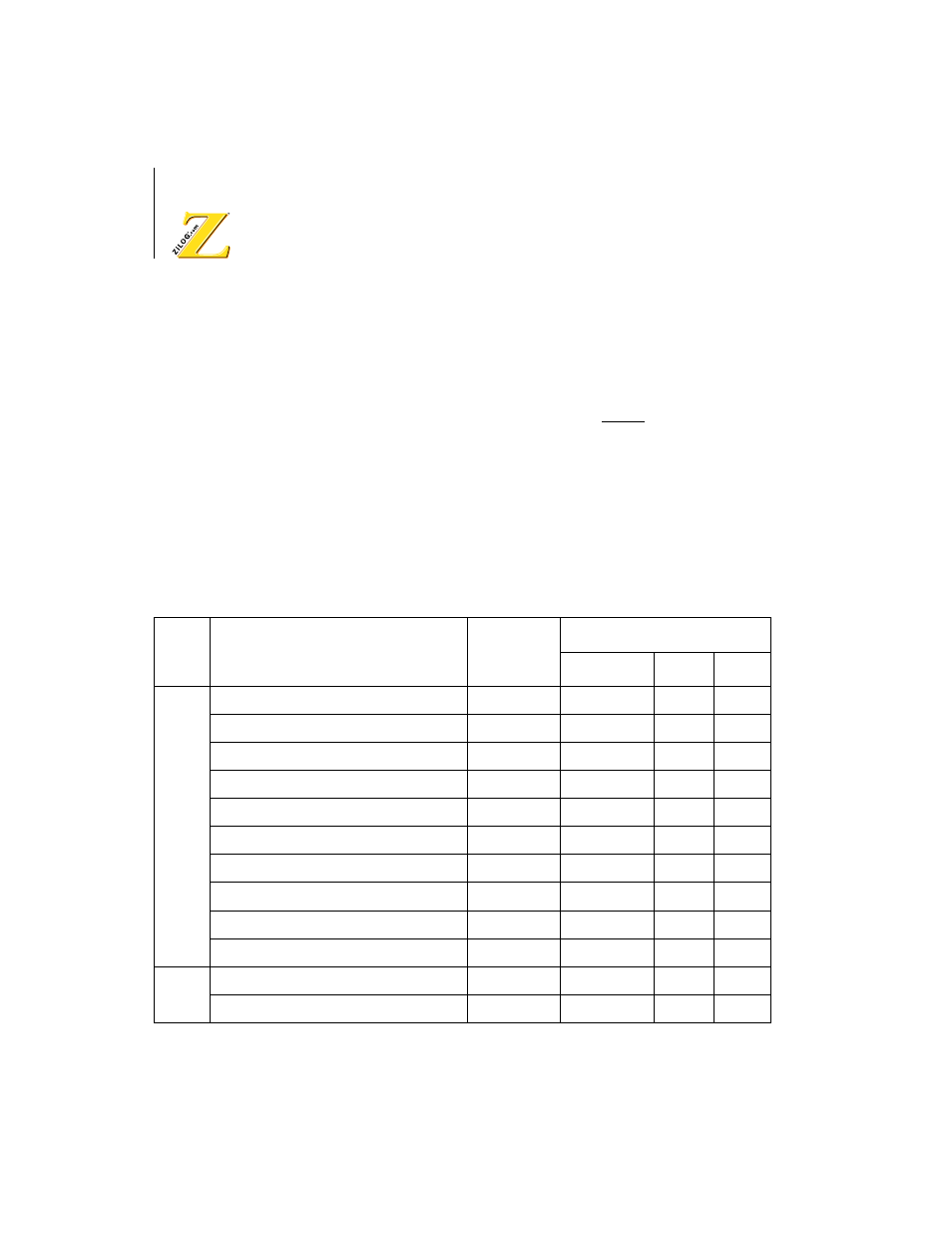

Table 6.

I/O Address Map for Z80180-Class Processors Only

Register

Mnemonic

Address

Binary

Hex

Page

ASCI

ASCI Control Register A Ch 0

CNTLA0

XX000000

00H

ASCI Control Register A Ch 1

CNTLA1

XX000001

01H

ASCI Control Register B Ch 0

CNTLB0

XX000010

02H

ASCI Control Register B Ch 1

CNTLB1

XX000011

03H

ASCI Status Register Ch 0

STAT0

XX000100

04H

ASCI Status Register Ch 1

STAT1

XX000101

05H

ASCI Transmit Data Register Ch 0

TDR0

XX000110

06H

ASCI Transmit Data Register Ch 1

TDR1

XX000111

07H

ASCI Receive Data Register Ch 0

RDR0

XX001000

08H

ASCI Receive Data Register Ch 1

RDR1

XX001001

09H

CSI/O CSI/O Control Register

CNTR

XX001010

0AH

CSI/O Transmit/Receive Data Register TRD

XX1011

0BH