Zilog Z80180 User Manual

Page 276

Z8018x

Family MPU User Manual

260

UM005003-0703

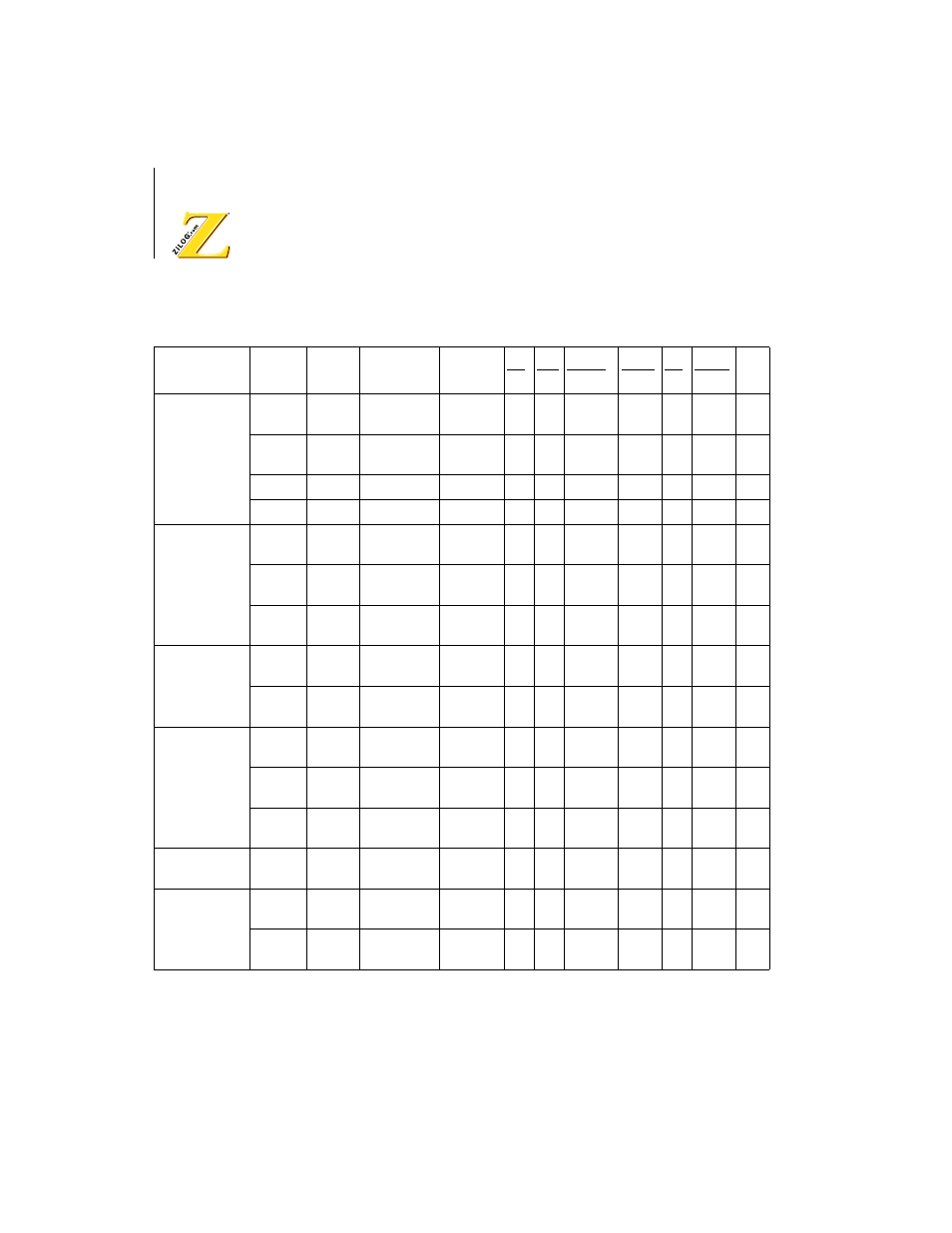

INIR

INDR

(If Br=0)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

T1T2T3 BC

DATA

0

1

1

0

1

1

1

MC4

T1T2T3 HL

DATA

1

0

0

1

1

1

1

JP mn

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 1st operand

Address

n

0

1

0

1

1

1

1

MC3

T1T2T3 2nd operand

Address

m

0

1

0

1

1

1

1

JP f,mn

(if is false)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 1st operand

Address

n

0

1

0

1

1

1

1

JP f,mn

(If f is true)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 1st operand

Address

n

0

1

0

1

1

1

1

MC3

T1T2T3 2nd operand

Address

m

0

1

0

1

1

1

1

JP (HL)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

JP (IX)

JP (IY)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

Instruction

Machine

Cycle

States

Address

Data

RD WR MREQ

IORQ M1 HALT ST