Zilog Z80180 User Manual

Page 284

Z8018x

Family MPU User Manual

268

UM005003-0703

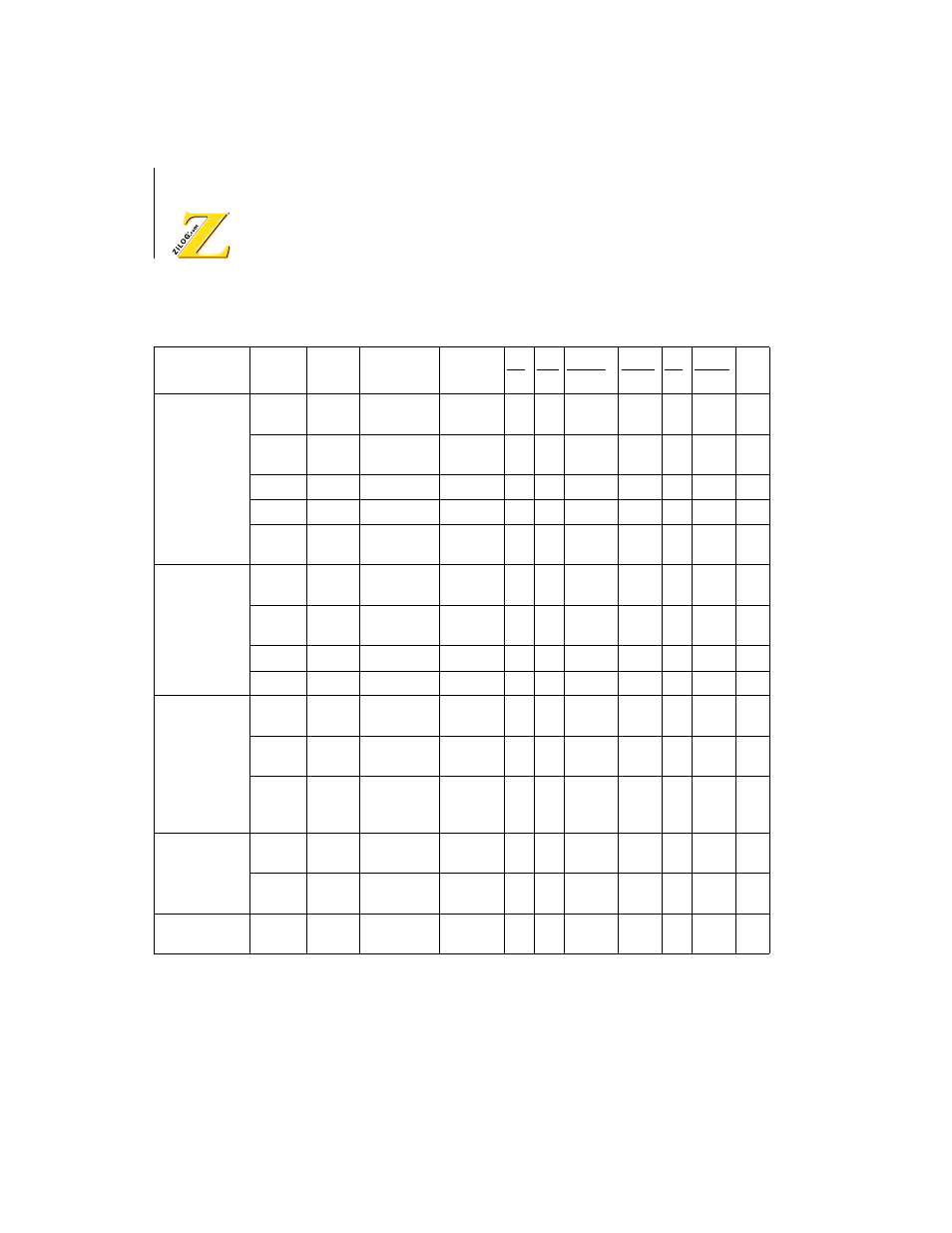

LDIR

LDDR

(If BCR

¹0)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

T1T2T3 HL

DATA

0

1

0

1

1

1

1

MC4

T1T2T3 DE

DATA

1

0

0

1

1

1

1

MC5~M

C6

TiTi

*

Z

1

1

1

1

1

1

1

LDIR

LDDR

(If BCR=0)

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

T1T2T3 HL

DATA

0

1

0

1

1

1

1

MC4

T1T2T3 DE

DATA

1

0

0

1

1

1

1

MLT ww**

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

~MC13

TiTiTTi

TiTiTiTi

TiTiTi

*

Z

1

1

1

1

1

1

1

NEG

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

NOP

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

Instruction

Machine

Cycle

States

Address

Data

RD WR MREQ

IORQ M1 HALT ST