R4 register, R5: fault status registers, R4 register r5: fault status registers – Digi NS9215 User Manual

Page 92: Access instructions register format register bits

W O R K I N G W I T H T H E C P U

R4 register

92

Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

R 4 r e g i s t e r

Accessing (reading or writing) this register causes

UNPREDICTABLE

behavior.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

R 5 : F a u l t S t a t u s r e g i s t e r s

Register R5 accesses the Fault Status registers (FSRs). The Fault Status registers

contain the source of the last instruction or data fault. The instruction-side FSR is

intended for debug purposes only.

The FSR is updated for alignment faults and for external aborts that occur while the

MMU is disabled. The FSR accessed is determined by the

opcode_2

value:

See "MemoryManagement Unit (MMU)," beginning on page 105, for the fault type

encoding.

Access

instructions

Access the FSRs using these instructions:

MRC p15, 0, Rd, c5, c0, 0; read DFSR

MCR p15, 0, Rd, c5, c0, 0; write DFSR

MRC p15, 0, Rd, c5, c0, 1; read IFSR

MCR p15, 0, Rd, c5, c0, 1; write IFSR

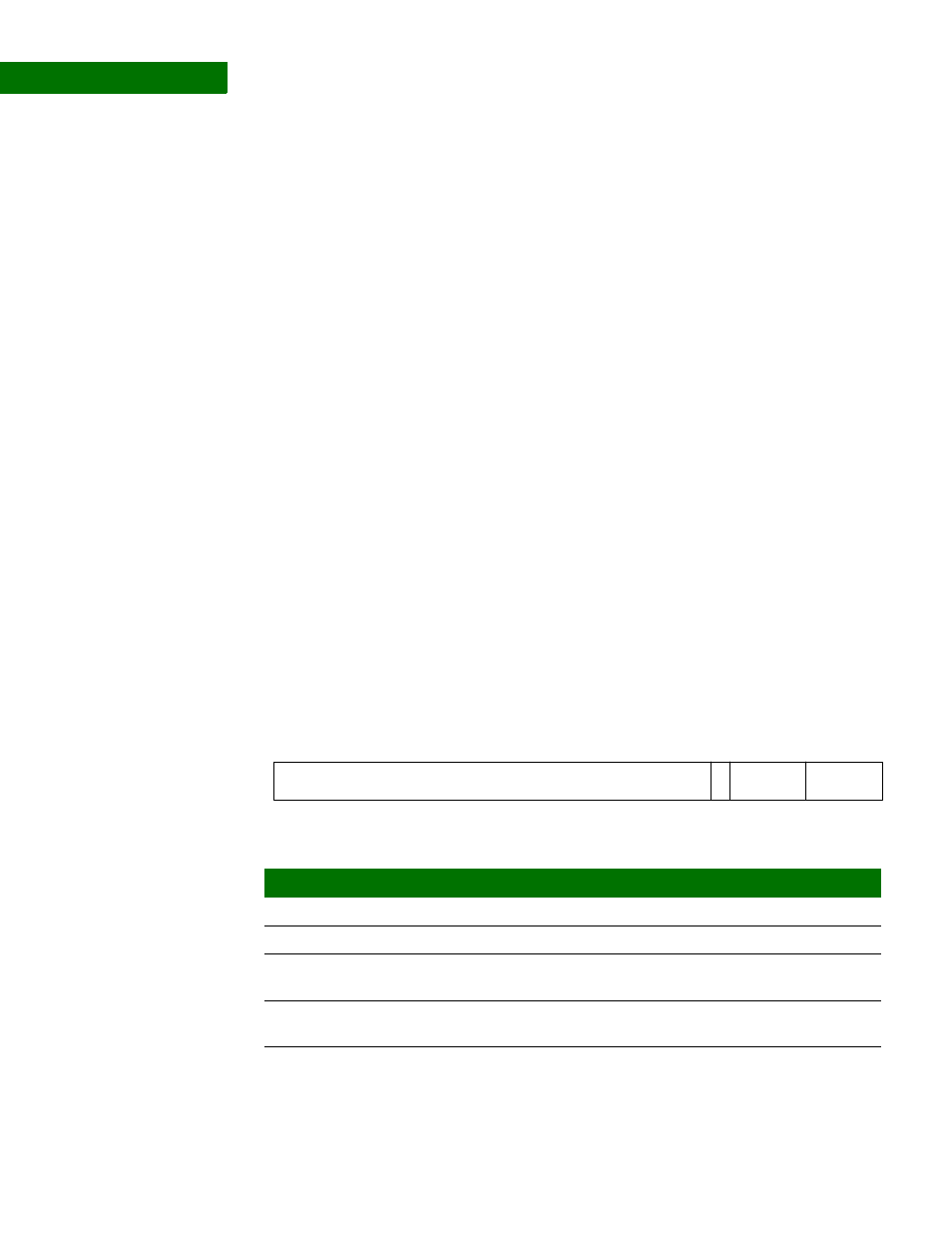

Register format

Register bits

opcode_2=0

Data Fault Status register (DFSR)

opcode_2=1

Instruction Fault Status register (IFSR)

31

0

9

8

7

4

3

0

UNP/SBZ

Domain

Status

Bits

Description

[31:9]

UNPREDICTABLE/SHOULD BE ZERO

[8]

Always reads as zero. Writes are ignored.

[7:4]

Specifies which of the 16 domains (D15–D0) was being accessed when a data fault

occurred.

[3:0]

Type of fault generated. (See "MemoryManagement Unit (MMU)," beginning on page

105.)