Digi NS9215 User Manual

Page 112

W O R K I N G W I T H T H E C P U

MemoryManagement Unit (MMU)

112

Hardware Reference NS9215

Section descriptor

bit description

Coarse page table

descriptor

A coarse page table descriptor provides the base address of a page table that

contains second-level descriptors for either large page or small page accesses.

Coarse page tables have 256 entries, splitting the 1 MB that the table describes into

4 KB blocks.

Note:

If a coarse page table descriptor is returned from the first-level fetch, a

second-level fetch is initiated.

Coarse page table

descriptor format

Coarse page table

descriptor bit

description

Fine page table

descriptor

A fine page table descriptor provides the base address of a page table that contains

second-level descriptors for large page, small page, or tiny page accesses. Fine

Bits

Description

[31:20]

Forms the corresponding bits of the physical address for a section.

[19:12]

Always written as 0.

[11:10]

Specify the access permissions for this section.

[09]

Always written as 0.

[8:5]

Specifies one of the 16 possible domains (held in the Domain and Access Control

register) that contain the primary access controls.

4

Should be written as 1, for backwards compatibility.

[3:2]

Indicate if the area of memory mapped by this section is treated as writeback cachable,

write-through cachable, noncached buffered, or noncached nonbuffered.

[1:0]

Must be 10 to indicate a section descriptor.

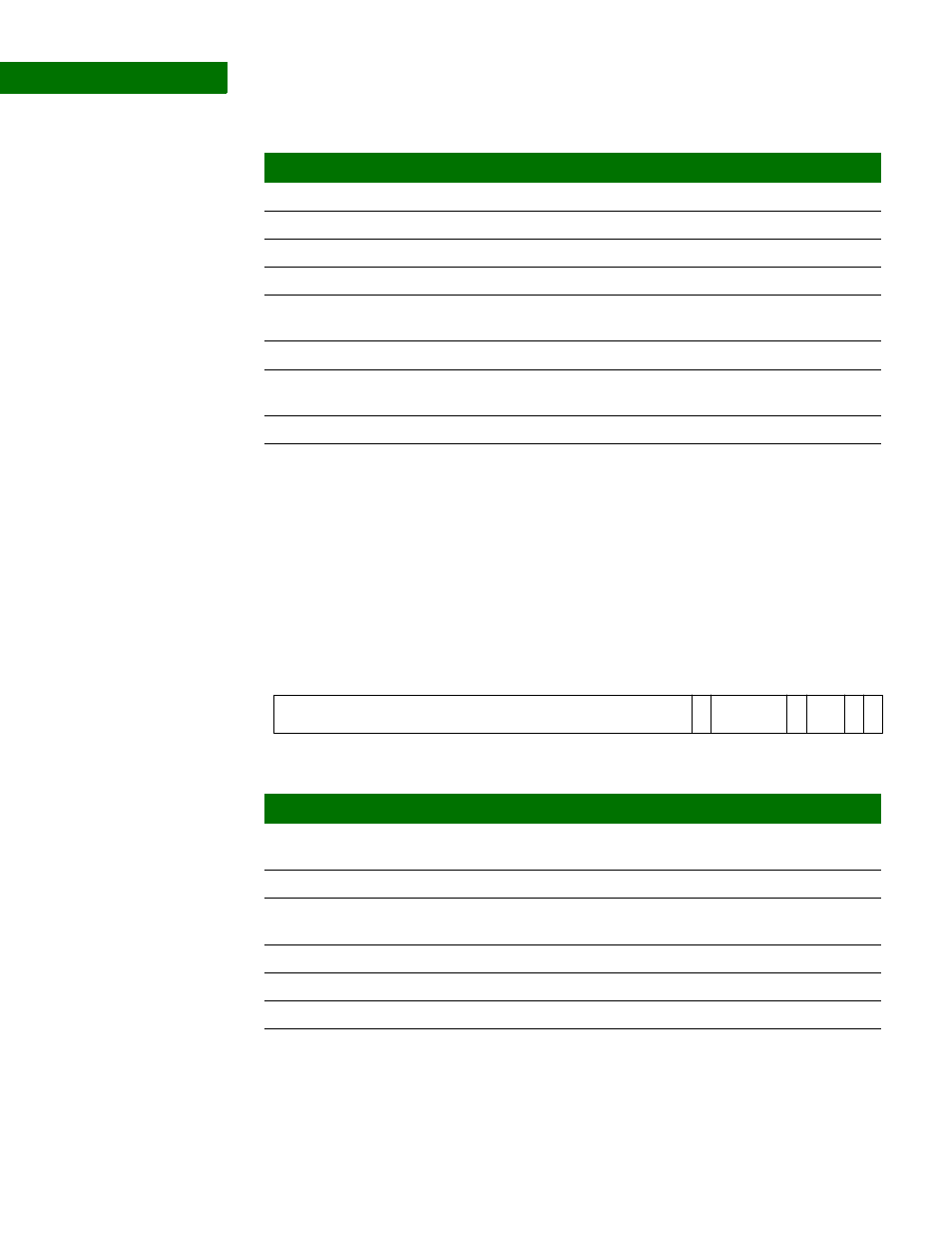

Coarse page table base address

S

B

Z

1

0

1

1

0

2

3

4

5

8

9

31

SBZ

10

Domain

Bits

Description

[31:10]

Forms the base for referencing the second-level descriptor (the coarse page table index

for the entry derived from the MVA).

9

Always written as 0.

[8:5]

Specifies one of the 16 possible domains (held in the Domain Access Control registers)

that contain the primary access controls.

4

Always written as 1.

[3:2]

Always written as 0.

[1:0]

Must be 01 to indicate a coarse page descriptor.