Mac configuration register #1 – Digi NS9215 User Manual

Page 288

E T H E R N E T C O M M U N I C A T I O N M O D U L E

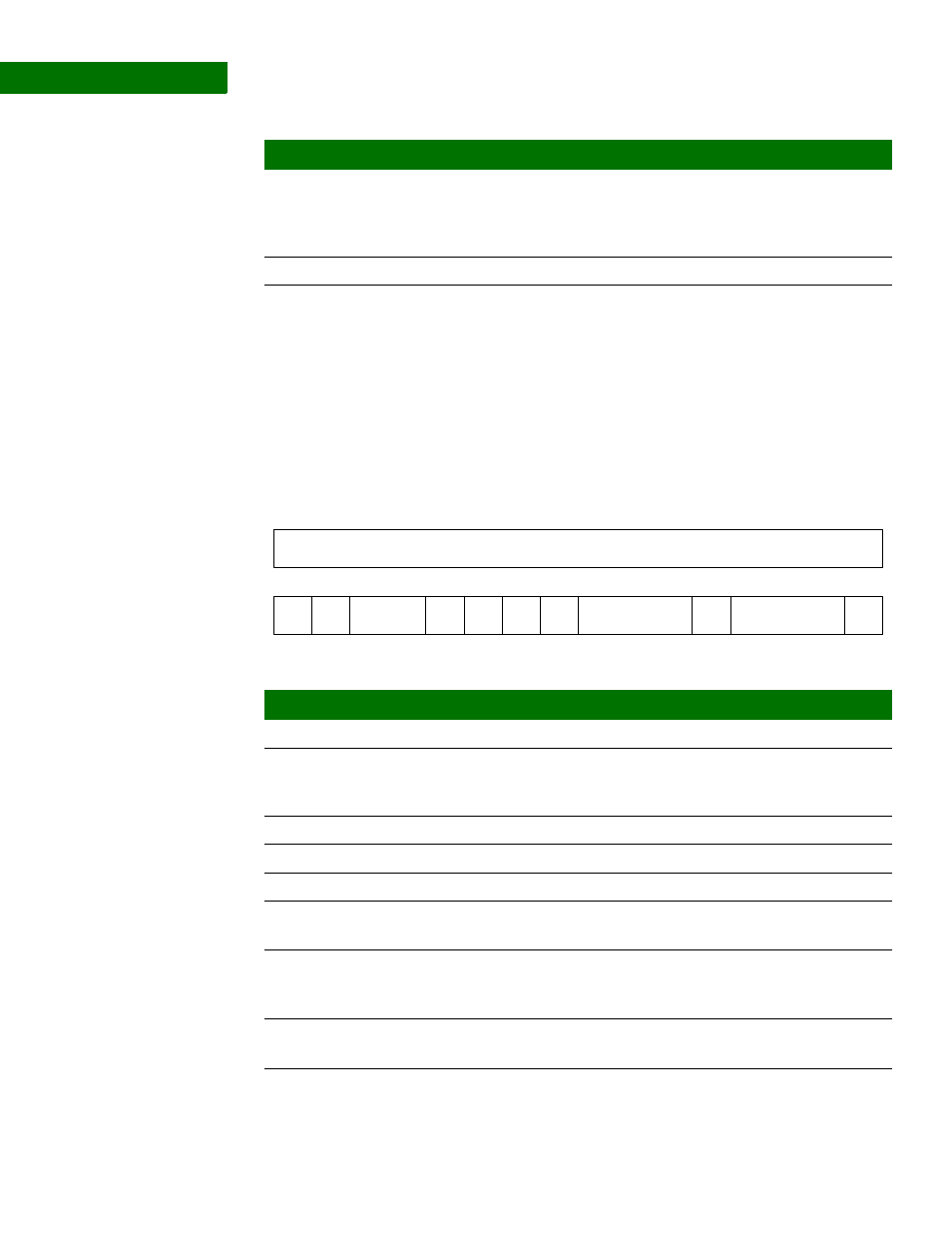

MAC Configuration Register #1

288

Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

M A C C o n f i g u r a t i o n R e g i s t e r # 1

Address: A060 0400

MAC Configuration Register #1 provides bits that control functionality within the

Ethernet MAC block.

Register

Register bit

assignment

D06

R

RXSHT

0x0

Receive frame is too short

Set when the frame’s length is less than 64 bytes.

Short frames are accepted only when the ERXSHT

bit is set to 1 in Ethernet General Control Register #1.

D05:00

N/A

Reserved

N/A

N/A

Bits

Access

Mnemonic

Reset

Description

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

SRST

Not

used

RPER

FUN

RPE

MCST

RPET

FUN

Reserved

LOOP

BK

RXEN

Not

used

Not used

Bits

Access

Mnemonic

Reset

Description

D31:16

N/A

Reserved

N/A

N/A

D15

R/W

SRST

1

Soft reset

Set this bit to 1 to reset the

RX_WR

,

TX_RD

, MAC

(except host interface), SAL (except host interface).

D14

R/W

Not used

0

Always write as 0.

D13:12

N/A

Reserved

N/A

N/A

D11

R/W

Not used

0

Always write as 0.

D10

R/W

RPERFUN

0

Reset PERFUN

Set this bit to 1 to put the MAC receive logic into reset.

D09

R/W

RPEMCST

0

Reset PEMCS/TX

Set this bit to 1 to put the MAC control

sublayer/transmit domain logic into reset.

D08

R/W

RPETFUN

0

Reset PETFUN

Set this bit to 1 to put the MAC transmit logic into reset.

D07:05

N/A

Reserved

N/A

N/A