Uart baud rate divisor lsb, Uart baud rate divisor msb – Digi NS9215 User Manual

Page 406

S E R I A L C O N T R O L M O D U L E : U A R T

UART Baud Rate Divisor LSB

406

Hardware Reference NS9215

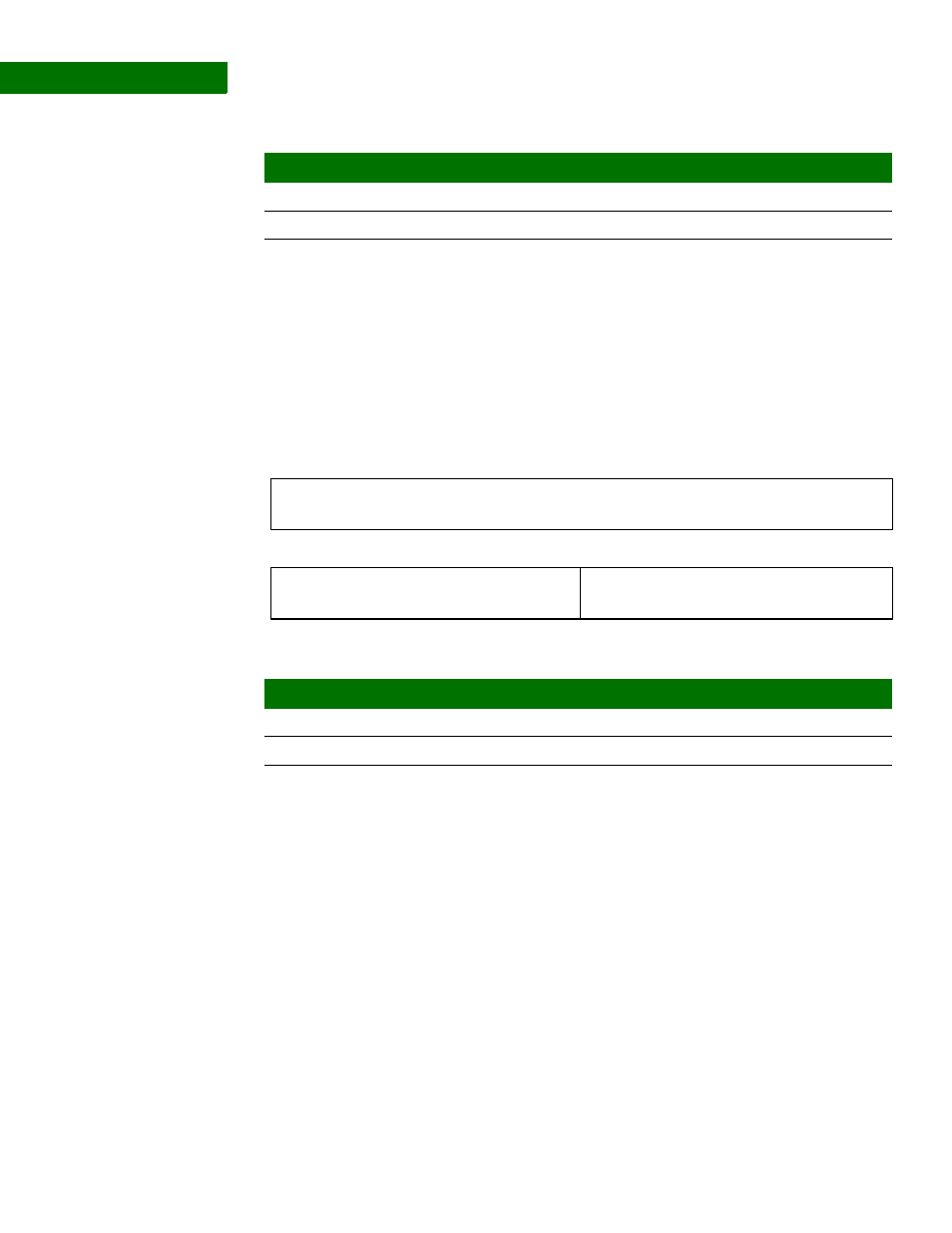

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

U A R T B a u d R a t e D i v i s o r L S B

Address: 9001_1100 / 9001_9100 / 9002_1100 / 9002_9100, DLAB = 1

UART Baud Rate Divisor sets bits 07:00 of the baud rate generator divisor.

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

U A R T B a u d R a t e D i v i s o r M S B

Address: 9001_1104 / 9001_9104 / 9002_1104 / 9002_9104, DLAB = 1

UART Baud Rate Divisor sets bits 15:08 of the baud rate generator divisor.

Bits

Access

Mnemonic

Reset

Description

D31:08

N/A

Reserved

N/A

N/A

D07:00

W

TBUFF

0

Transmitter data bits

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Reserved

BRDL

Bits

Access

Mnemonic

Reset

Description

D31:08

N/A

Reserved

N/A

N/A

D07:00

R/W

BRDL

0x1

Bits 07:00 of the baud rate generator divisor