Digi NS9215 User Manual

Page 120

W O R K I N G W I T H T H E C P U

MMU faults and CPU aborts

120

Hardware Reference NS9215

register. If an access violation simultaneously generates more than one source of

abort, the aborts are encoded in the priority shown in the priority encoding table.

The Fault Address register is not updated by faults caused by instruction prefetches.

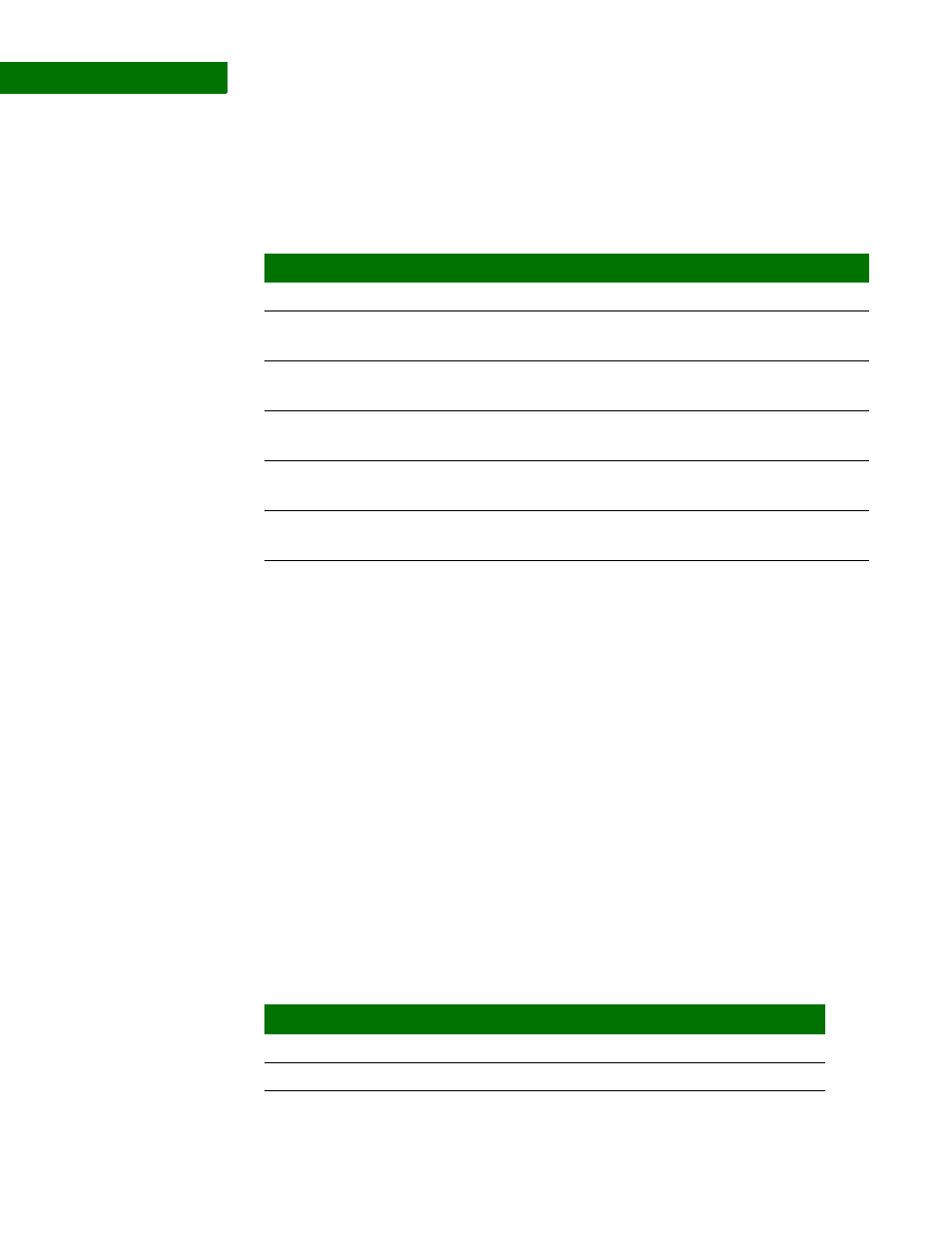

Priority encoding

table

Notes:

Alignment faults can write either

0b0001

or

0b0011

into Fault Status register

[3:0]

.

Invalid values can occur in the status bit encoding for domain faults. This

happens when the fault is raised before a valid domain field has been read

from a page table description.

Aborts masked by a higher priority abort can be regenerated by fixing the

cause of the higher priority abort, and repeating the access.

Alignment faults are not possible for instruction fetches.

The Instruction Fault Status register can be updated for instruction prefetch

operations

(

MCR p15,0,Rd,c7,c13,1

)

.

Fault Address

register (FAR)

For load and store instructions that can involve the transfer of more than one word

(

LDM/STM, STRD,

and

STC/LDC

), the value written into the Fault Address register

depends on the type of access and, for external aborts, on whether the access

crosses a 1 KB boundary.

FAR values for

multi-word

transfers

Priority

Source

Size

Status

Domain

Highest

Alignment

---

0b00x1

Invalid

External abort on transmission

First level

Second level

0b1100

0b1110

Invalid

Valid

Translation

Section page

0b0101

0b0111

Invalid

Valid

Domain

Section page

0b1001

0b1011

Valid

Valid

Permission

Section page

0b1101

0b1111

Valid

Valid

Lowest

External abort

Section page

0b1000

0b1010

Valid

Valid

Domain

Fault Address register

Alignment

MVA of first aborted address in transfer

External abort on translation

MVA of first aborted address in transfer

Translation

MVA of first aborted address in transfer