Register register bit assignment – Digi NS9215 User Manual

Page 252

M E M O R Y C O N T R O L L E R

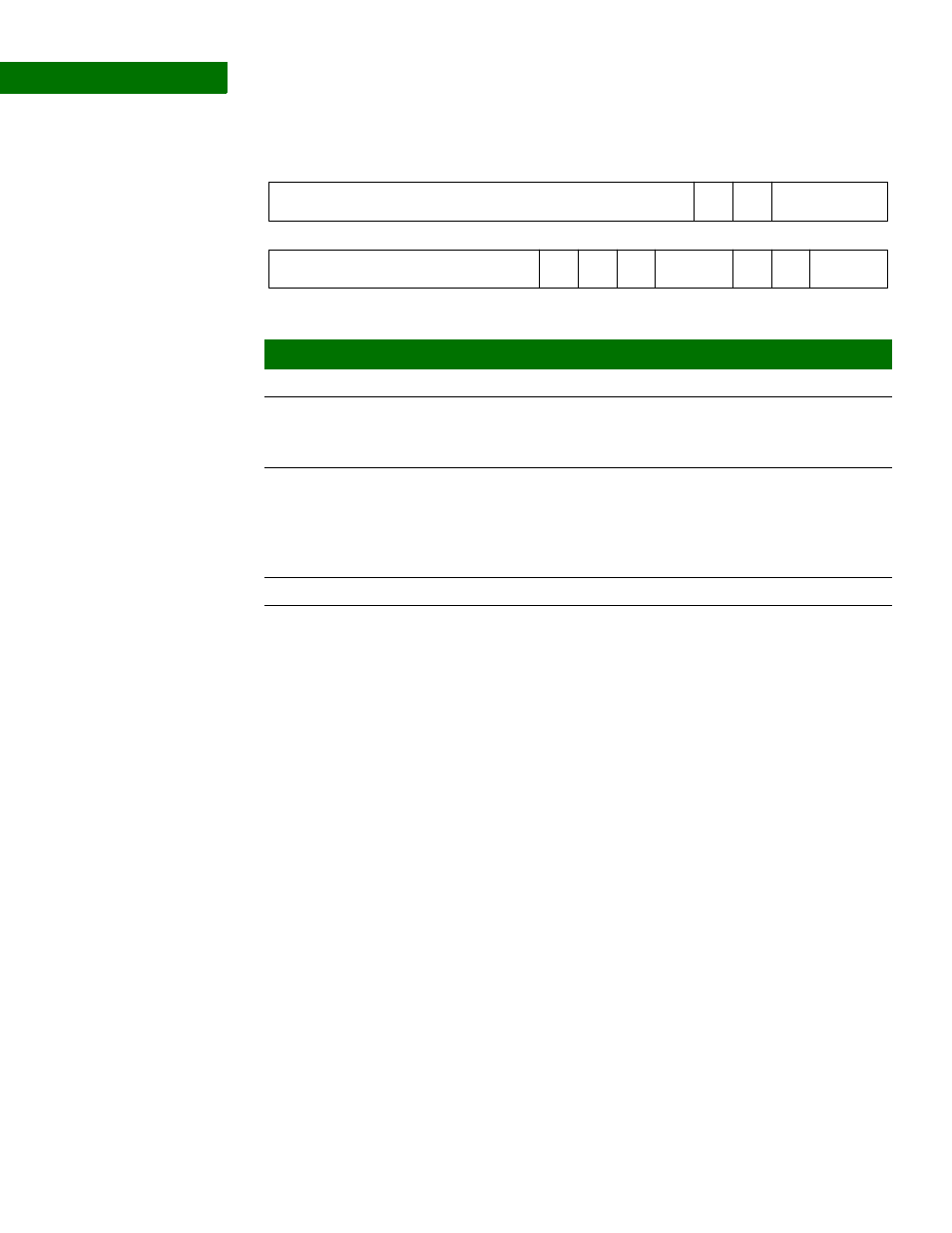

StaticMemory Configuration 0–3 registers

252

Hardware Reference NS9215

Register

Register bit

assignment

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

PSMC

BSMC

Reserved

Reserved

EW

PB

PC

Reserved

PM

BMODE

MW

Bits

Access

Mnemonic

Description

D31:21

N/A

Reserved

N/A (do not modify)

D20

R/W

PSMC

Write protect

0

Writes not protected (reset value on

reset_n

)

1

Write protected

D19

R/W

BSMC

Buffer enable

0

Write buffer disabled (reset value on

reset_n

)

1

Write buffer enabled

Note:

This field must always be set to 0 when a peripheral other

than SRAM is attached to the static ram chip select.

D18:09

N/A

Reserved

N/A (do not modify)

D08

R/W

EW

Extended wait

0

Extended wait disabled (reset value on

reset_n

)

1

Extended wait enabled

Extended wait uses the Static Extended Wait register to time both

the read and write transfers, rather than the Static Memory Read

Delay 0–3 registers and Static Memory Write Delay 0–3 registers.

This allows much longer transactions.

Extended wait also can be used with the

ns_ta_strb

signal to allow a

slow peripheral to terminate the access. In this case, the Static

Memory Extended Wait register can be programmed with the

maximum timeout limit. A high value on

ns_ta_strb

is then used to

terminate the access before the maximum timeout occurs.

Note:

Extended wait and page mode cannot be selected simulta-

neously.