Digi NS9215 User Manual

Page 116

W O R K I N G W I T H T H E C P U

MemoryManagement Unit (MMU)

116

Hardware Reference NS9215

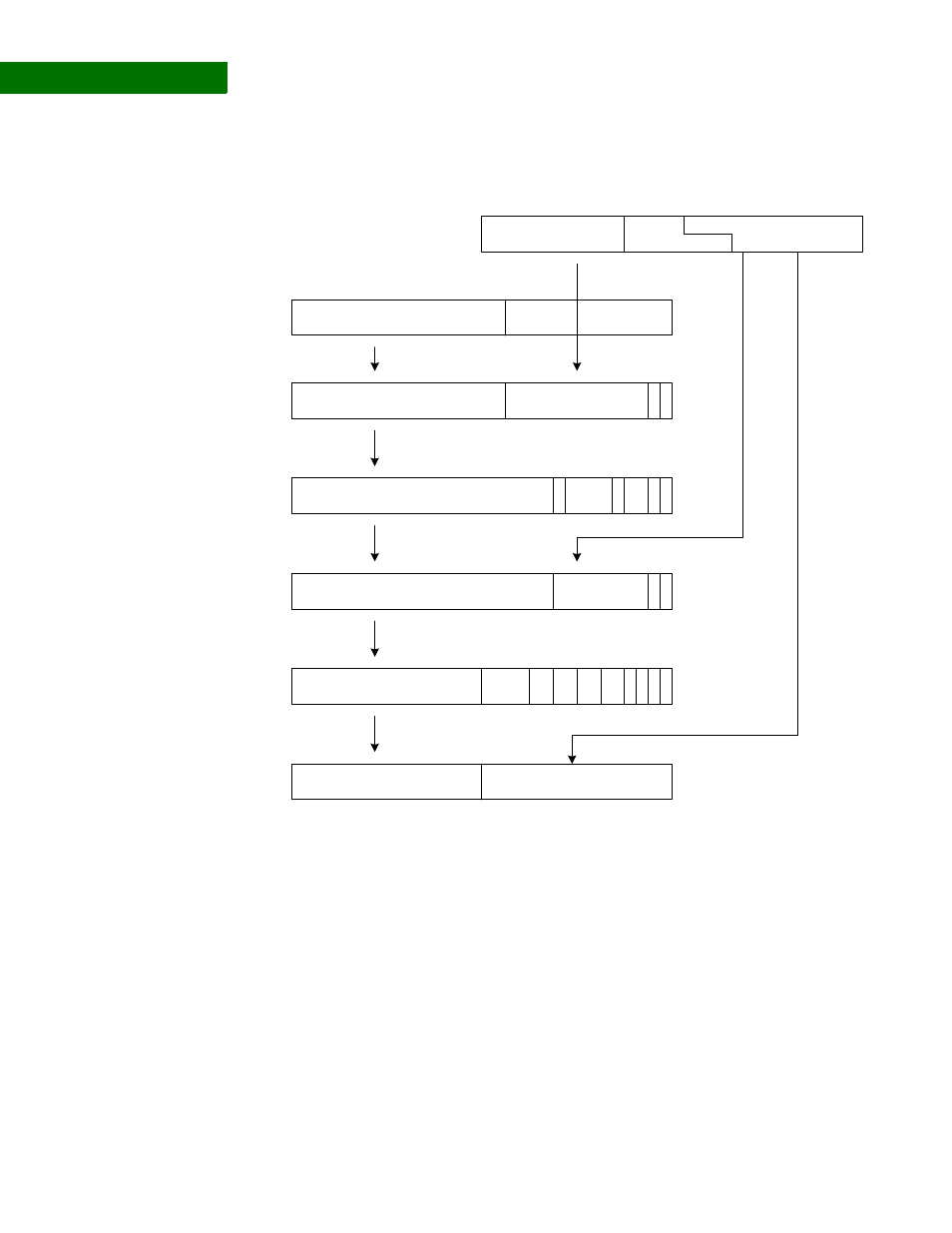

Translation

sequence for large

page references

Because the upper four bits of the page index and low-order four bits of the coarse

page table index overlap, each coarse page table entry for a large page must be

duplicated 16 times (in consecutive memory locations) in the coarse page table.

If the large page descriptor is included in a fine page table, the high-order six bits

of the page index and low-order six bits of the fine page table overlap. Each fine

page table entry for a large page must be duplicated 64 times.

31

14 13

0

Translation base

1

Translation table base

31

14 13

0

Translation base

2

Table index

0 0

31

20 19

0

Table index

Page index

First-level descriptor

31

0

Coarse page table base address

2

0 1

1

3

4

5

Domain 1

31

0

Coarse page table base address

table index

1615

12 11

Modified virtual address

8

9

10

1

2

9

10

31

1615

12 1110 9 8 7 6 5 4 3 2 1 0

0

0

L2 table index

0 1

B

C

AP0

AP1

AP2

AP3

Page base address

Page base address

31

0

16 15

Page index

Physical address

Second-level descriptor