Ethernet transmit status register, Register register bit assignment – Digi NS9215 User Manual

Page 284

E T H E R N E T C O M M U N I C A T I O N M O D U L E

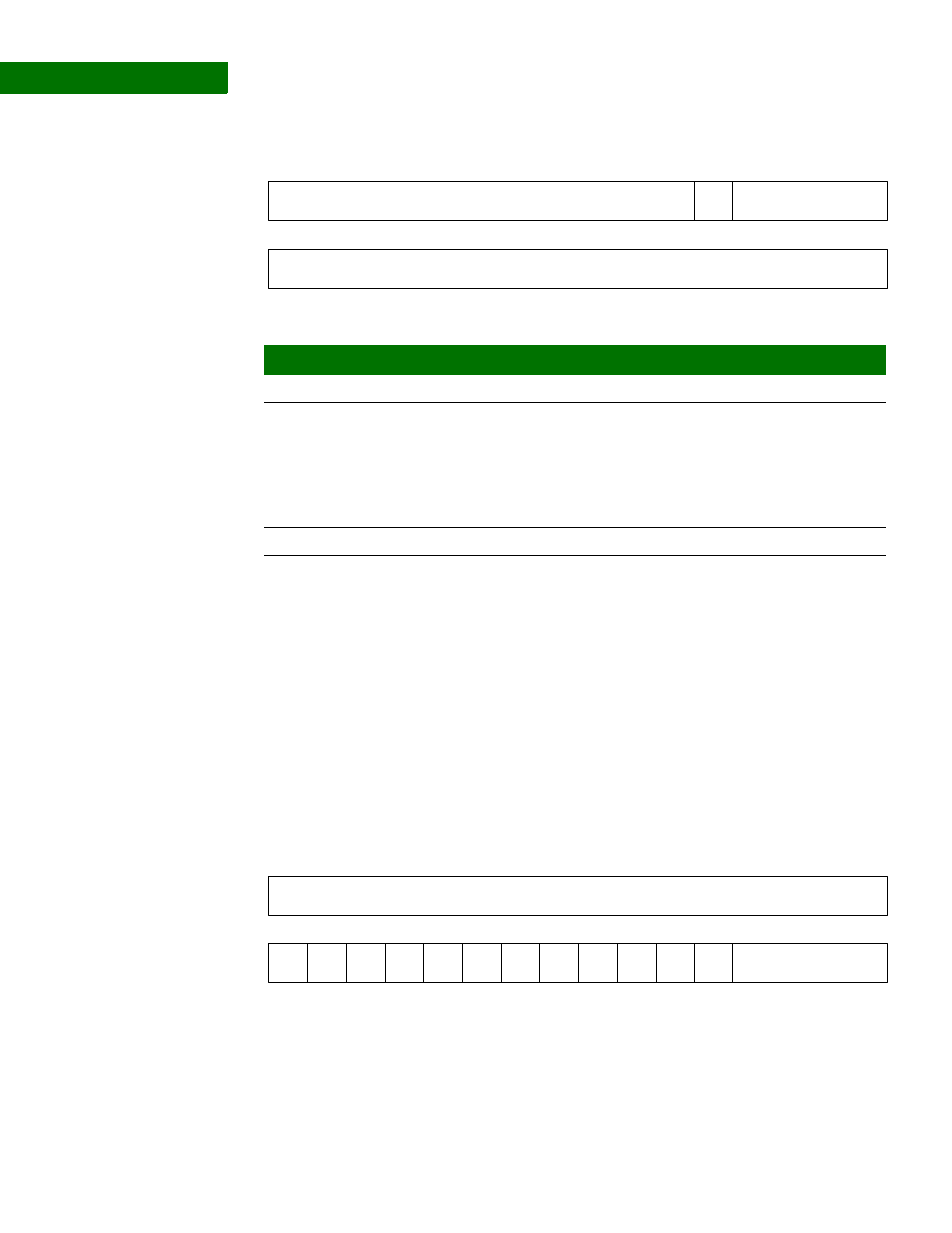

Ethernet Transmit Status register

284

Hardware Reference NS9215

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E t h e r n e t T r a n s m i t S t a t u s r e g i s t e r

Address: A060 0018

The Ethernet Status register contains the status for the last transmit frame. The

TXDONE bit in the Ethernet Interrupt Status register (see page 317) is set upon

completion of a transmit frame and the Ethernet Transmit Status register is loaded

at the same time. Bits [15:0] are also loaded into the Status field of the last

transmit buffer descriptor for the frame.

Register

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

RX

INIT

Reserved

Bits

Access

Mnemonic

Reset

Description

D31:21

N/A

Reserved

N/A

N/A

D20

R/C

RXINIT

0x0

RX initialization complete

Set when the

RX_RD

logic has completed the

initialization of the local buffer descriptor registers

requested when ERXINIT in Ethernet General

Control Register #1 is set. The delay from ERXINIT

set to RXINIT set is less than five microseconds.

D19:00

N/A

Reserved

N/A

N/A

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Not

used

TX

DEF

TX

CRC

Not

used

TXCOLC

TX

OK

TX

BR

TX

MC

TX

AL

TX

AED

TX

AEC

TX

AUR

TX

AJ