Mac configuration register #2 – Digi NS9215 User Manual

Page 289

. . . . .

E T H E R N E T C O M M U N I C A T I O N M O D U L E

MAC Configuration Register #2

www.digiembedded.com

289

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

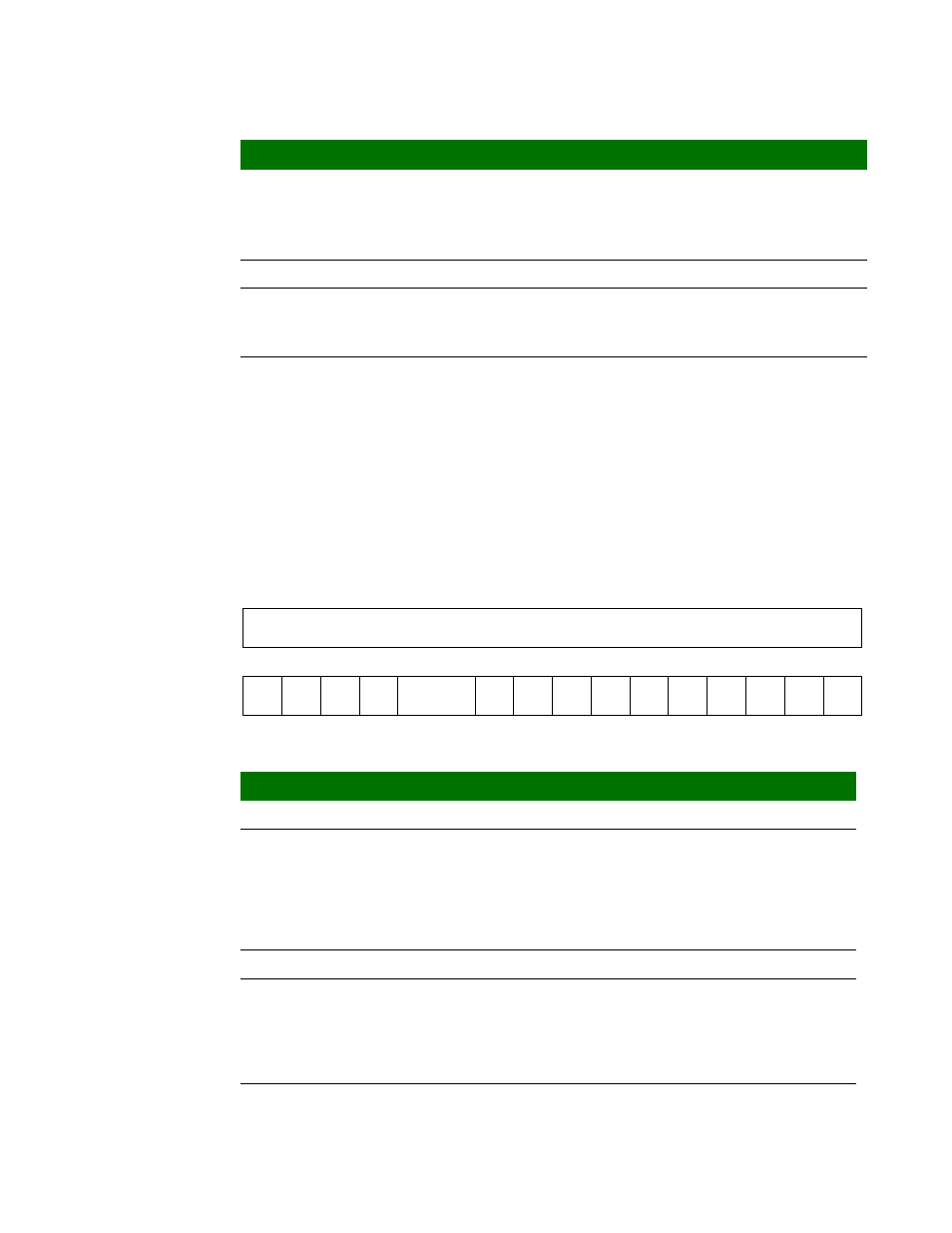

M A C C o n f i g u r a t i o n R e g i s t e r # 2

Address: A060 0404

MAC Configuration Register #2 provides additional bits that control functionality

within the Ethernet MAC block.

Register

Register bit

assignment

D04

R/W

LOOPBK

0

Internal loopback

Set this bit to 1 to cause the MAC transmit interface to

be internally looped back to the MAC receive interface.

Clearing this bit results in normal operation.

D03:01

R/W

Not used

0

Always write as 0.

D00

R/W

RXEN

0

Receive enable

Set this bit to 1 to allow the MAC receiver to receive

frames.

Bits

Access

Mnemonic

Reset

Description

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Rsvd

EDE

FER

LONGP PUREP

CRCEN

Not

used

HUGE

Not

used

FULLD

Not

used

NOBO

AUTOP VLANP PADEN

Bits

Access

Mnemonic

Reset

Definition

D31:15

N/A

Reserved

N/A

N/A

D14

R/W

EDEFER

0

Excess deferral

0

The MAC aborts when the excessive deferral limit is

reached (that is, 6071 nibble times in 100 Mbps mode

or 24,287 bit times in 10 Mbps mode).

1

Enables the MAC to defer to carrier indefinitely, as

per the 802.3u standard.

D13

R/W

Not used

0

Always write to 0.

D12

R/W

NOBO

0

No backoff

When this bit is set to 1, the MAC immediately

retransmits following a collision, rather than using the

binary exponential backoff algorithm (as specified in the

802.3u standard).

D11:10

N/A

Reserved

N/A

N/A