Interrupt enable register – Digi NS9215 User Manual

Page 468

R E A L T I M E C L O C K M O D U L E

Interrupt Enable register

468

Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

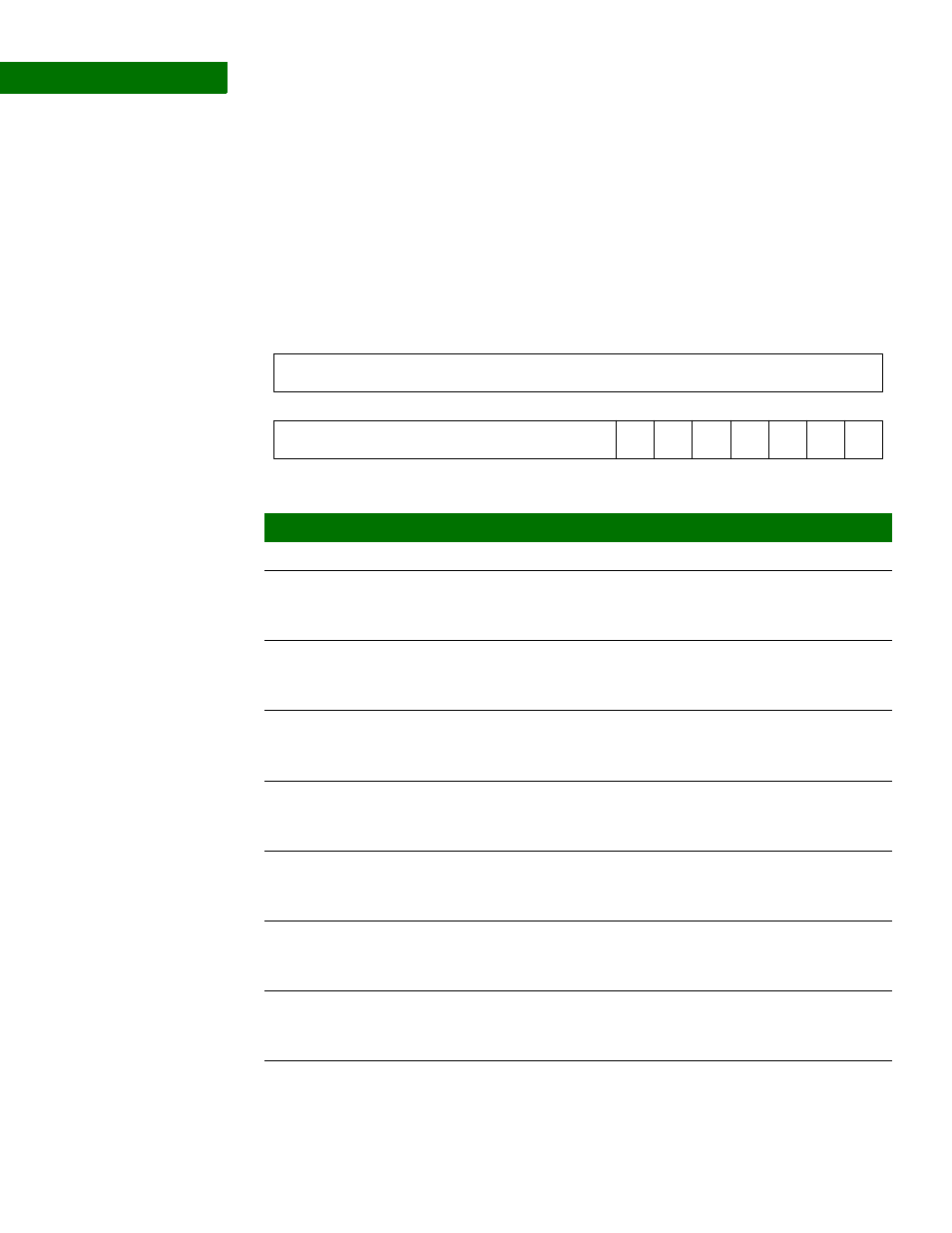

I n t e r r u p t E n a b l e r e g i s t e r

Address: 9006 0020

The Interrupt Enable register sets which events can generate and interrupt. The

interrupt that is generated remains set until it is cleared by disabling the event or

by reading/clearing the Event Flags register.

Register

Register bit

assignment

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Reserved

Mnth

Int

Date

Int

Hour

Int

Min

Int

Sec

Int

Hsec

Int

Alrm

Int

Bits

Access

Mnemonic

Reset

Description

D31:07

N/A

Reserved

N/A

N/A

D06

W

Alrm Int

0x0

Alarm interrupt

0

Disable alarm interrupt

1

Enable alarm interrupt

D05

W

Mnth Int

0x0

Month interrupt

0

Disable month interrupt

1

Enable month interrupt

D04

W

Date Int

0x0

Date interrupt

0

Disable date interrupt

1

Enable date interrupt

D03

W

Hour Int

0x0

Hour interrupt

0

Disable hour interrupt

1

Enable hour interrupt

D02

W

Min Int

0x0

Minute interrupt

0

Disable minute interrupt

1

Enable minute interrupt

D01

W

Sec Int

0x0

Second interrupt

0

Disable second interrupt

1

Enable second interrupt

D00

W

Hsec Int

0x0

Hundredth of a second interrupt

0

Disable hundredth second interrupt

1

Enable hundredth second interrupt