I2c registers, Command transmit data register, Register address map – Digi NS9215 User Manual

Page 450: Register

I 2 C M A S T E R / S L A V E I N T E R F A C E

I2C registers

450

Hardware Reference NS9215

bus owner, the transaction goes through. If the module loses bus arbitration, an

M_ARBIT_LOST

interrupt is generated to the host processor and the command must

be reissued.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

2

C r e g i s t e r s

All registers have 8-bit definitions, but must be accessed in pairs. For example,

TX_DATA_REG

and

CMD_REG

are written simultaneously and

RX_DATA_REG

and

STATUS_REG

are read simultaneously.

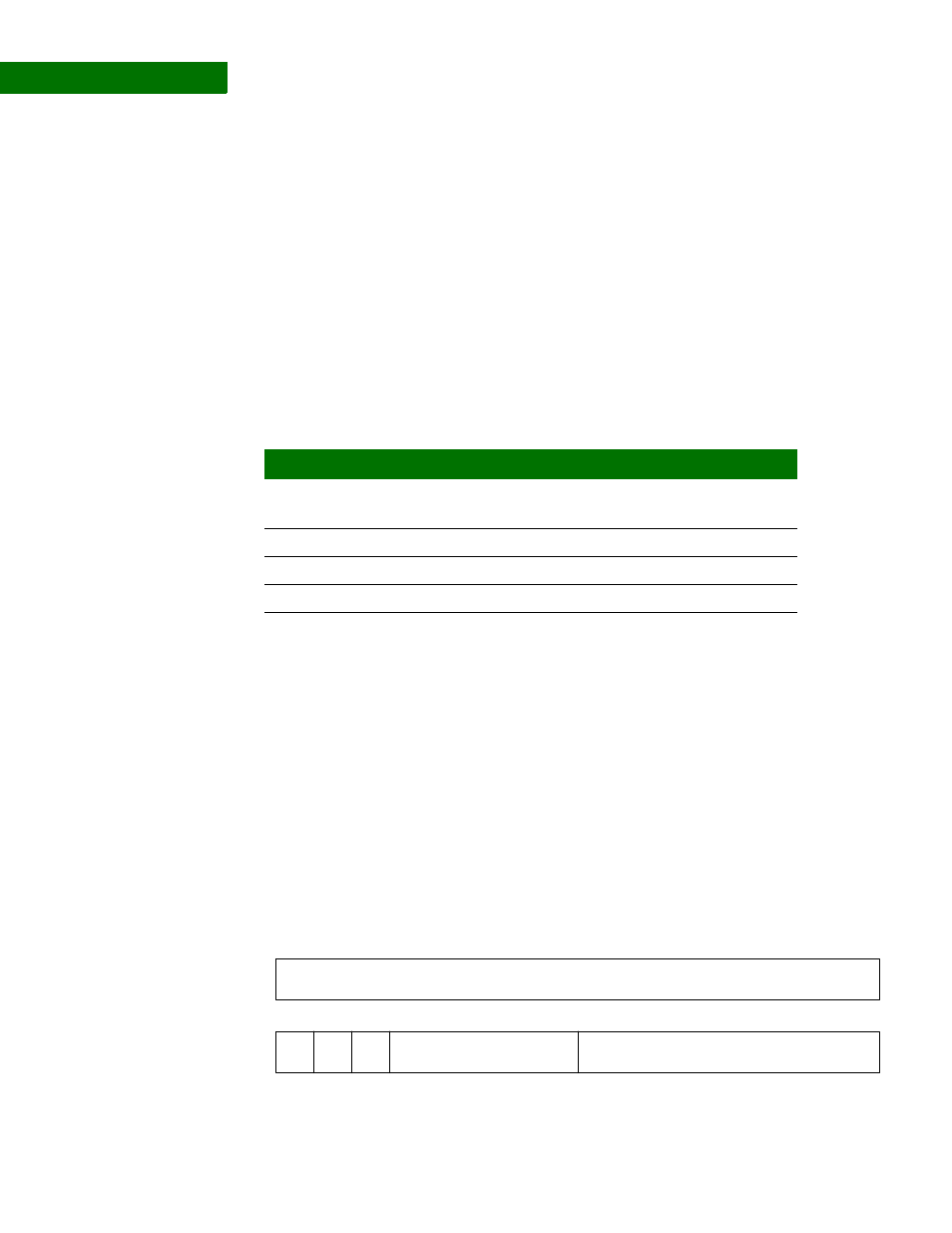

Register address

map

This table shows the register addresses. All configuration registers must be accessed

as 32-bit words and as single accesses only. Bursting is not allowed.

After a reset, all registers are set to the initial value. If an unspecified register or

bit is read, a zero is returned.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C o m m a n d T r a n s m i t D a t a r e g i s t e r

Address: 9005 0000

The Command Transmit Data (

CMD_TX_DATA_REG

) register is the primary interface

register for transmission of data between the I/O hub and I

2

C bus. This register is

write only.

Register

Register

Description

9005 0000

Command Transmit Data register (

CMD_TX_DATA_REG

)

Status Receive Data register (

STATUS_RX_DATA_REG

)

9005 0004

Master Address register

9005 0008

Slave Address register

9005 000C

Configuration register

TXVAL

CMD

TXDATA

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

PIPE

DLEN

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved