Multicast address filter enable register – Digi NS9215 User Manual

Page 331

. . . . .

E T H E R N E T C O M M U N I C A T I O N M O D U L E

Multicast Address Filter Enable register

www.digiembedded.com

331

Multicast High

Address Mask

Register #5

Address: A060 0AB4

Multicast High

Address Mask

Register #6

Address: A060 0AB8

Multicast High

Address Mask

Register #7

Address: A060 0ABC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

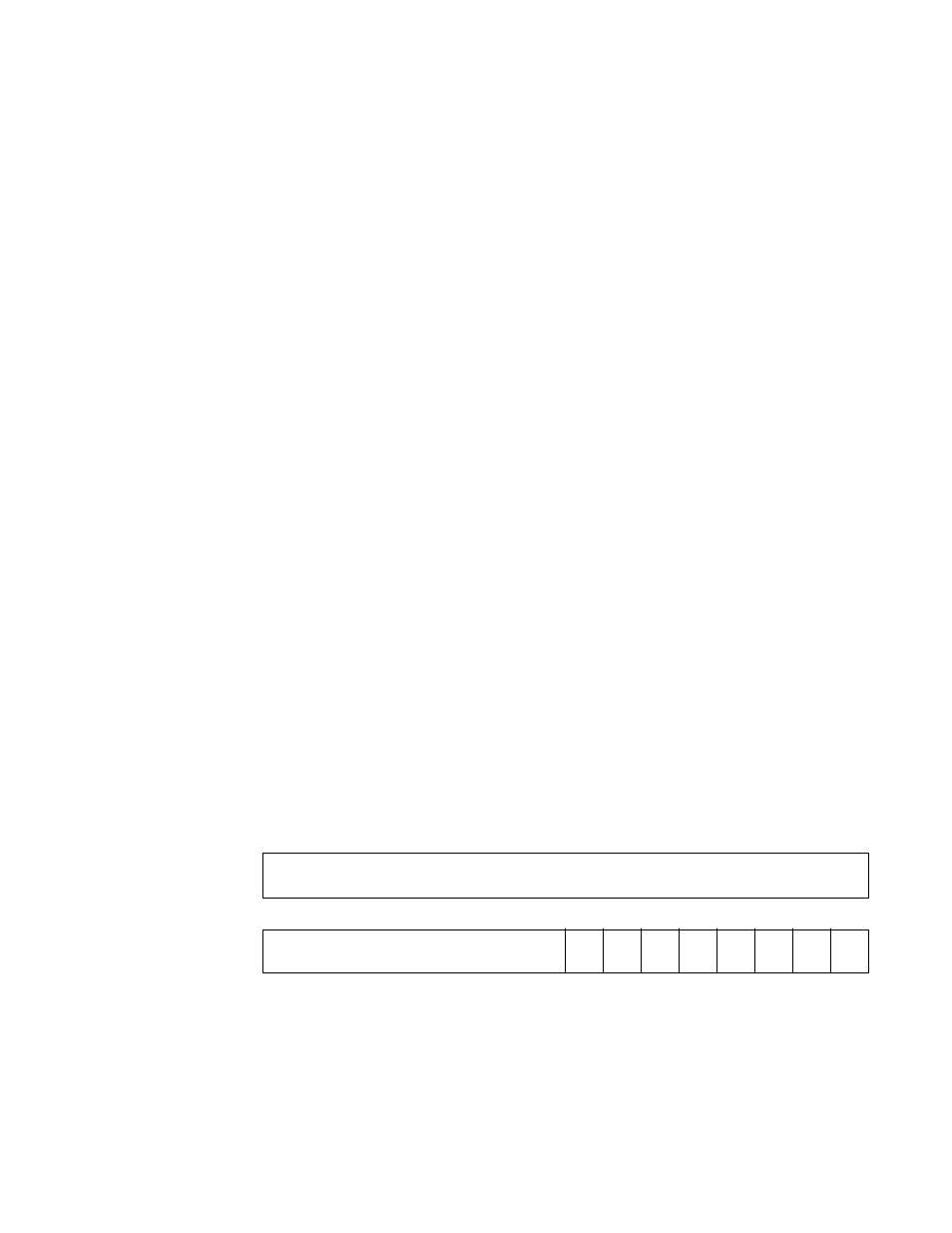

M u l t i c a s t A d d r e s s F i l t e r E n a b l e r e g i s t e r

Address: A060 0AC0

The Multicast Address Filter Enable register individually enables each of the eight

entries in the multicast address filter logic. For an explanation of the

synchronization scheme used for this register, see “Clock synchronization” on

page 276.

Register

D15:00

R/W

Default = 0x0000 0000

MFMSKH4

D31:16

R

Default = 0x0000 0000

Reserved (read as 0)

D15:00

R/W

Default = 0x0000 0000

MFMSKH5

D31:16

R

Default = 0x0000 0000

Reserved (read as 0)

D15:00

R/W

Default = 0x0000 0000

MFMSKH6

D31:16

R

Default = 0x0000 0000

Reserved (read as 0)

D15:00

R/W

Default = 0x0000 0000

MFMSKH7

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Reserved

MFILT

EN7

MFILT

EN6

MFILT

EN5

MFILT

EN4

MFILT

EN3

MFILT

EN2

MFILT

EN1

MFILT

EN0