Clock timing, System pll reference clock timing – Digi NS9215 User Manual

Page 511

. . . . .

T I M I N G

Clock timing

www.digiembedded.com

511

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C l o c k t i m i n g

All AC characteristics are measured with 10pF, unless otherwise noted.

System PLL

reference clock

timing

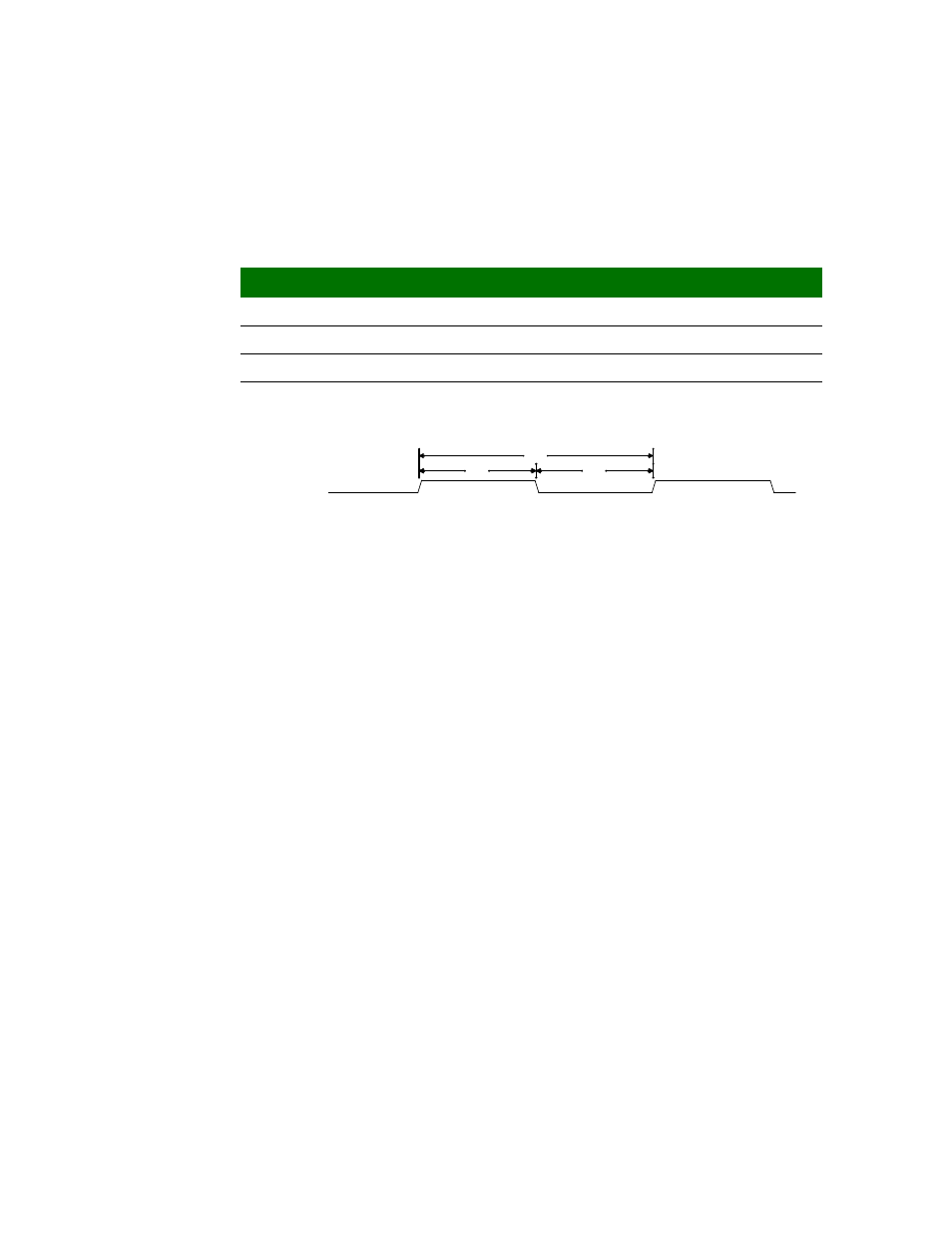

The diagram below pertains to clock timing.

Parm

Description

Min

Max

Unit

Notes

SC1

x1_sys_osc cycle time

25

50

ns

SC2

x1_sys_osc high time

(SC1/2) x 0.45

(SC1/2) x 0.55

ns

SC3

x1_sys_osc low time

(SC1/2) x 0.45

(SC1/2) x 0.55

ns

SC1

SC2

SC2

SC3

SC1

SC3

x1_sys_osc