Module] dma rx buffer descriptor pointer – Digi NS9215 User Manual

Page 376

I / O H U B M O D U L E

[Module] DMA RX Buffer Descriptor Pointer

376

Hardware Reference NS9215

31 March 2008

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

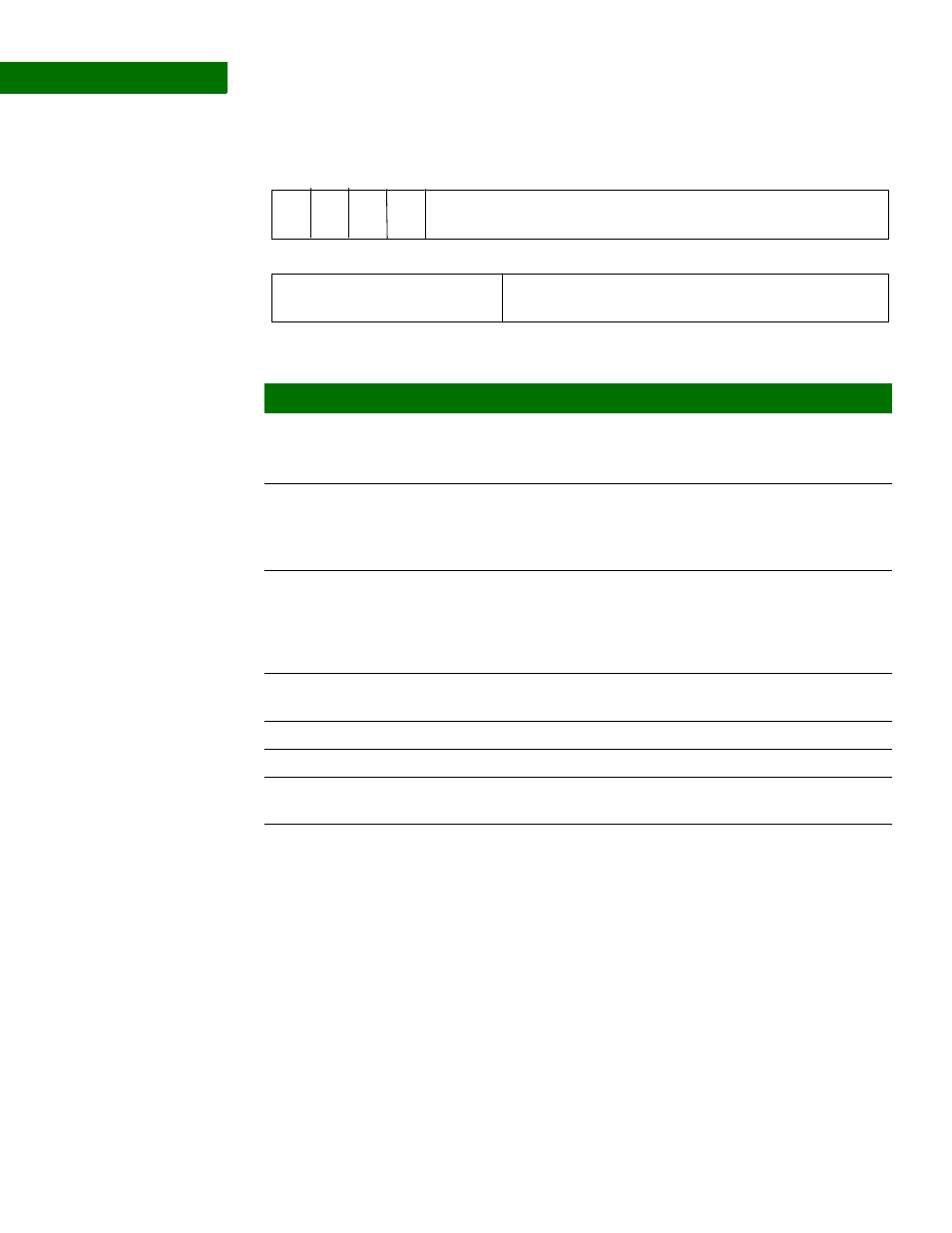

[ M o d u l e ] D M A R X B u f f e r D e s c r i p t o r P o i n t e r

Addresses: 9000_0008 / 9000_8008 / 9001_0008 / 9001_8008 / 9002_0008 /

9002_8008 / 9003_0008 / 9003_8008

The DMA RX Buffer Descriptor Pointer register is the address of the first buffer

descriptor for each DMA channel.

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

INDEX

CE

CA FLEX

I/O

DIRECT

Reserved

STATE

Bit(s)

Access

Mnemonic

Reset

Description

D31

R/W

CE

0x0

Channel enable

0

Disable DMA operation

1

Enable DMA operation

D30

R/W

CA

0x0

Channel abort

When set, causes the current DMA operation to

complete and closes the buffer. The DMA channel

remains idle until this bit is cleared.

D29

R/W

FLEX I/O

0x0

0

DMA controlled by CPU

1

DMA controlled by flexible I/O

This bit is valid only for channels 0 and 1, which

are assigned to flexible I/O module 0 and

flexible I/O module 1.

D28

R/W

DIRECT

0x0

0

DMA mode

1

Direct access mode

D27:16

N/A

Reserved

N/A

N/A

D15:10

R

STATE

0x0

DMA state machine status field

D09:00

R

INDEX

0x0

This field can be read at any time to determine the

current index.