Status register, Configuration register, Status register configuration register – Digi NS9215 User Manual

Page 234

M E M O R Y C O N T R O L L E R

Status register

234

Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

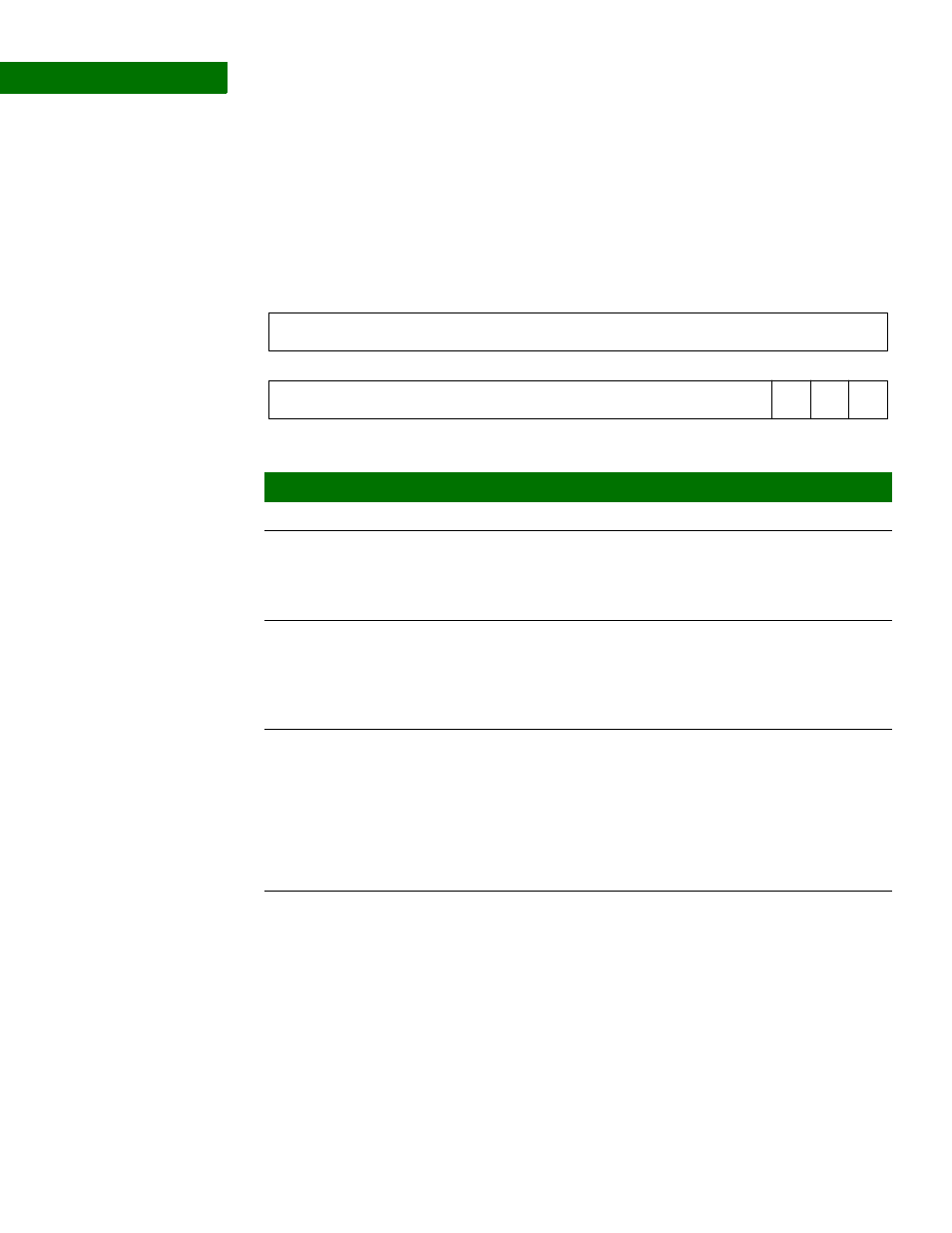

S t a t u s r e g i s t e r

Address: A070 0004

The Status register provides memory controller status information.

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C o n f i g u r a t i o n r e g i s t e r

Address: A070 0008

The Configuration register configures memory controller operation. It is

recommended that this register be modified during system initialization, or when

there are no current or outstanding transactions. Wait until the memory controller

is idle, then enter low-power or disabled mode.

BUSY

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Reserved

SA

WBS

Bits

Access

Mnemonic

Description

D31:03

N/A

Reserved

N/A (do not modify)

D02

R

SA

Self-refresh acknowledge (SREFACK)

0

Normal mode

1

Self refresh mode (reset value on

reset_n

)

Indicates the memory controller operating mode.

D01

R

WBS

Write buffer status

0

Write buffers empty (reset value on

reset_n

)

1

Write buffers contain data

Enables the memory controller to enter low-power mode or

disabled mode clearly.

D00

R

BUSY

Busy

0

Memory controller is idle

1

Memory controller is busy performing memory transactions,

commands, or auto-refresh cycles, or is in self-refresh mode

(reset value on

reset_n

).

Ensures that the memory controller enters the low-power or

disabled state cleanly by determining whether the memory

controller is busy.