Dma status and interrupt enable register – Digi NS9215 User Manual

Page 350

E X T E R N A L D M A

DMA Status and Interrupt Enable register

350

Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

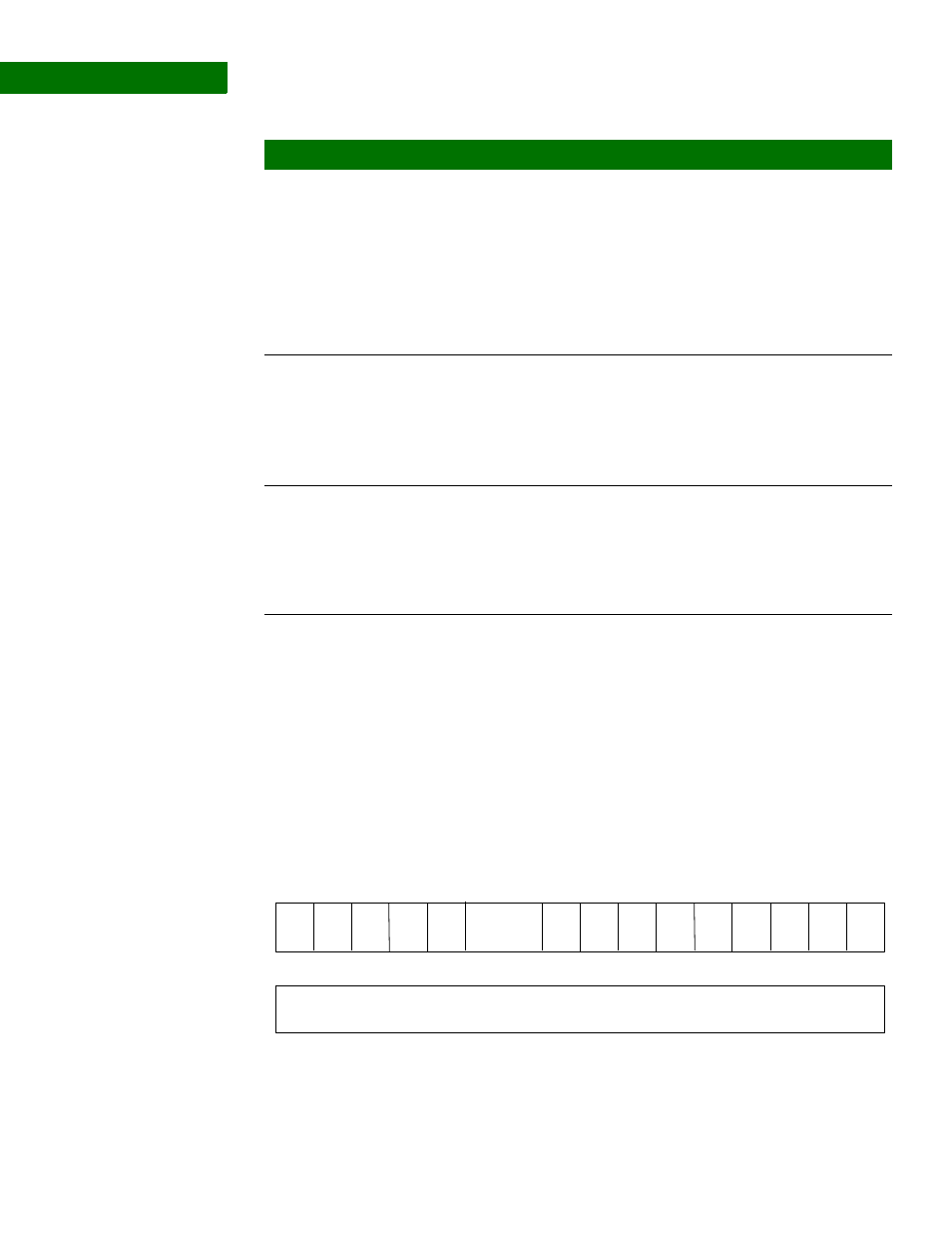

D M A S t a t u s a n d I n t e r r u p t E n a b l e r e g i s t e r

Address: A080_0008, A080_0018

The DMA Status and Interrupt Enable register contains the DMA transfer status and

control information used in generating AHB DMA interrupt signals. The external DMA

module has two of these registers.

Register

D16

R/W

RST

0

Reset

Forces a reset of the DMA channel. Writing a 1 to

this field forces all fields in this register, except the

index field, to the reset state. The reset field is

written with the value specified on signals

HWDATA[9:0]. This field always reads back a 0.

Note:

Writing a 1 to this field while the DMA

channel is operational will have unpre-

dictable results.

D15:10

R

STATE

0

State

0

Idle

1-3

Buffer descriptor read

4-7

Data transfer

8-12

Buffer descriptor update

13

Error

D09:00

R/W

INDEX

0

Index

Identifies the current 16-byte offset pointer

relative to the buffer descriptor pointer.

Note:

This field can be written to only when

the RST field (D16) is being written to a

1.

Bit(s)

Access

Mnemonic

Reset

Description

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

NCIP

ECIP NRIP

CAIP

Not

used

NCIE

CAIE

PCIE

WRAP

FULL

LAST

DONE

PCIP

ECIE NRIE

BLEN