Mii management indicators register, Register register bit assignment – Digi NS9215 User Manual

Page 299

. . . . .

E T H E R N E T C O M M U N I C A T I O N M O D U L E

MII Management Indicators register

www.digiembedded.com

299

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

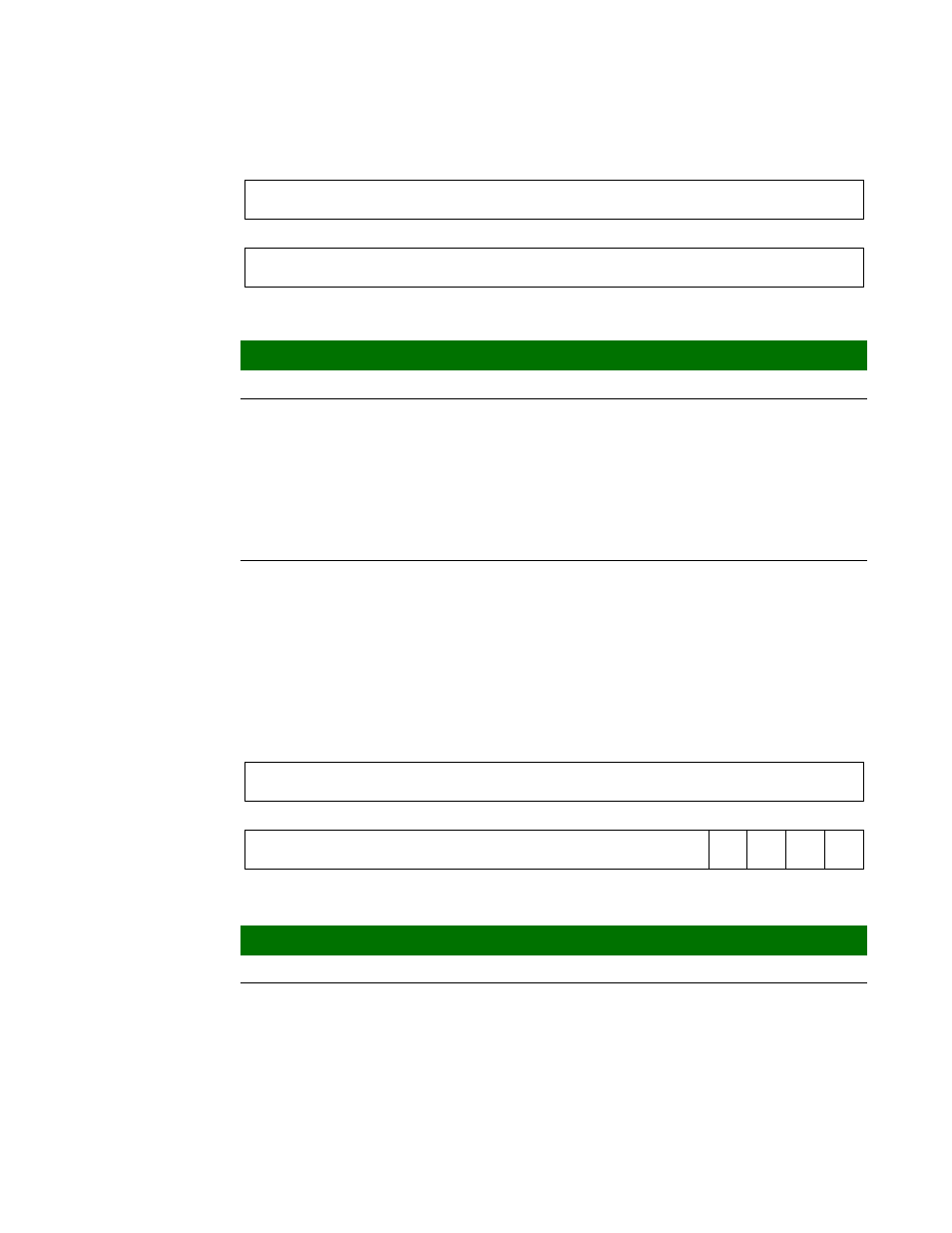

M I I M a n a g e m e n t I n d i c a t o r s r e g i s t e r

Address: A060 0434

Register

Register bit

assignment

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

MRDD

Bits

Access

Mnemonic

Reset

Description

D31:16

N/A

Reserved

N/A

N/A

D15:00

R

MRDD

0x0000

MII read data

Read data is obtained by reading from this register

after an MII Management read cycle. An MII

Management read cycle is executed by loading the

MII Management Address register, then setting the

READ bit to 1 in the MII Management Command

register. Read data is available after the BUSY bit in

the MII Management Indicators register returns to 0.

Reserved

MIILF

BUSY

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

N

VALID SCAN

Bits

Access

Mnemonic

Reset

Description

D31:04

N/A

Reserved

N/A

N/A

D03

R

MIILF

0

MII link failure

When set to 1, indicates that the PHY currently has a

link fail condition.