Mii management address register, Register register bit assignment – Digi NS9215 User Manual

Page 297

. . . . .

E T H E R N E T C O M M U N I C A T I O N M O D U L E

MII Management Address register

www.digiembedded.com

297

Register

Register bit

assignment

Note:

If both SCAN and READ are set, SCAN takes precedence.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

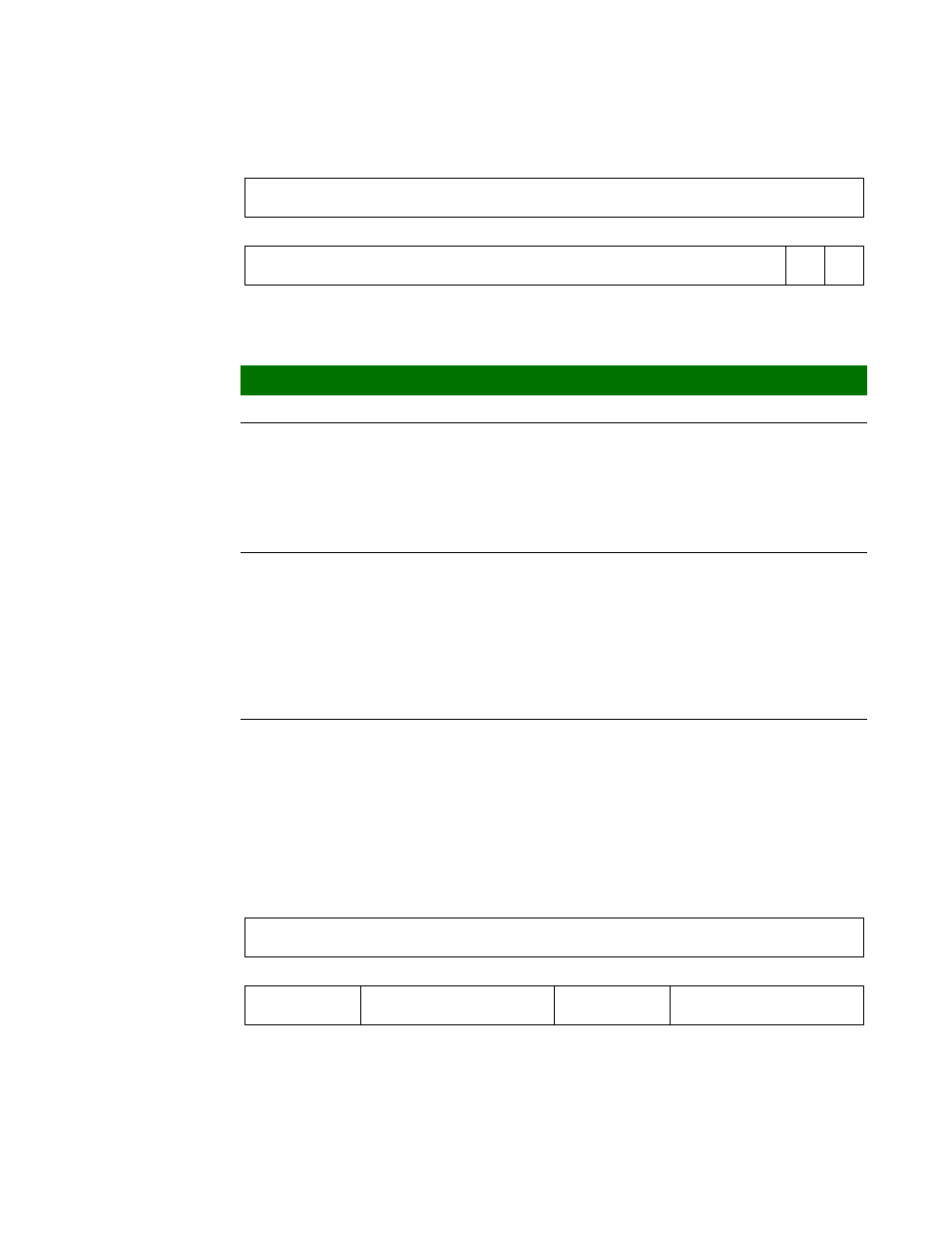

M I I M a n a g e m e n t A d d r e s s r e g i s t e r

Address: A060 0428

Register

Reserved

READ

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

SCAN

Bits

Access

Mnemonic

Reset

Description

D31:02

N/A

Reserved

N/A

N/A

D01

R/W

SCAN

0

Automatically scan for read data

Set to 1 to have the MII Management module perform

read cycles continuously. This is useful for

monitoring link fail, for example.

Note:

SCAN must transition from a 0 to a 1 to

initiate the continuous read cycles.

D00

R/W

READ

0

Single scan for read data

Set to 1 to have the MII Management module perform

a single read cycle. The read data is returned in the

MII Management Read Data register after the BUSY

bit in the MII Management Indicators register has

returned to a value of 0.

Note:

READ must transition from a 0 to a 1 to

initiate a single read cycle.

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

DADR

Reserved

Reserved

RADR