Digi NS9215 User Manual

Page 410

S E R I A L C O N T R O L M O D U L E : U A R T

UART Line Control register

410

Hardware Reference NS9215

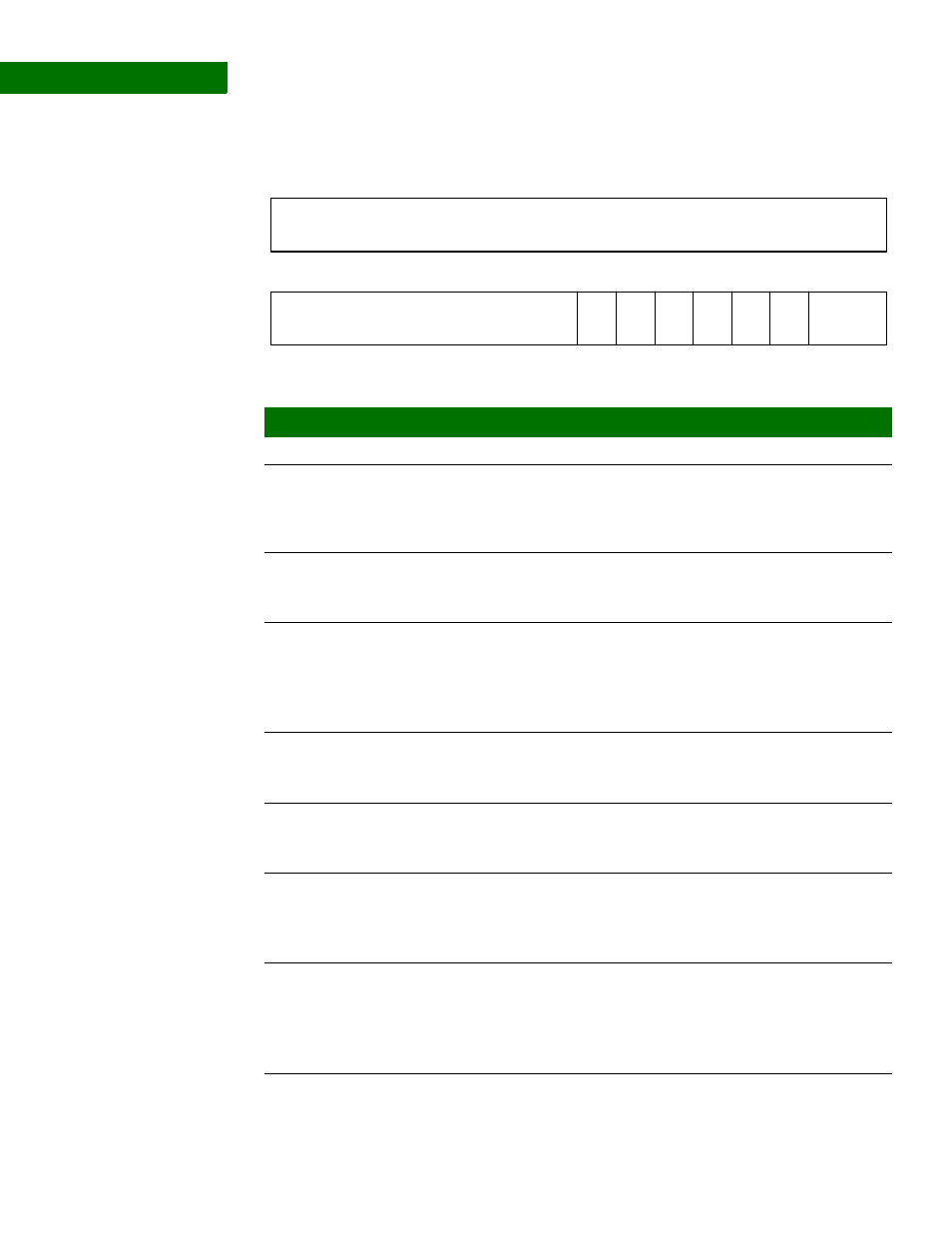

Register

Register bit

assignment

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Reserved

DLAB

SB

SP

EPS

PEN

STB

WLS

Bits

Access

Mnemonic

Reset

Description

D31:08

N/A

Reserved

N/A

N/A

D07

R/W

DLAB

0

Divisor latch access bit

0

Disabled

1

Enabled. Enables the Baud Rate Divisor MSB and

LSB registers to be configured.

D06

R/W

SB

0

Set break, if set TX data is set to 0

0

Disabled

1

Enabled

D05

R/W

SP

0

Stick parity, operates as follows

When set bits 04:03 = 11, parity bit always set to 0

When set bits 04:03 = 00, parity bit always set to 1

0

Disabled

1

Enabled

D04

R/W

EPS

0

Parity select

0

Odd parity

1

Even parity

D03

R/W

PEN

0

Parity enable

0

Parity disabled

1

Parity enabled

D02

R/W

STB

0

Number of stop bits

0

1 stop bit

1

1.5 stop bits (WLS = 00)

2 stop bits (all other WLS settings)

D01:00

R/W

WLS

0

Word length select

00

5 bits

01

6 bits

10

7 bits

11

8 bits