Digi NS9215 User Manual

Page 373

. . . . .

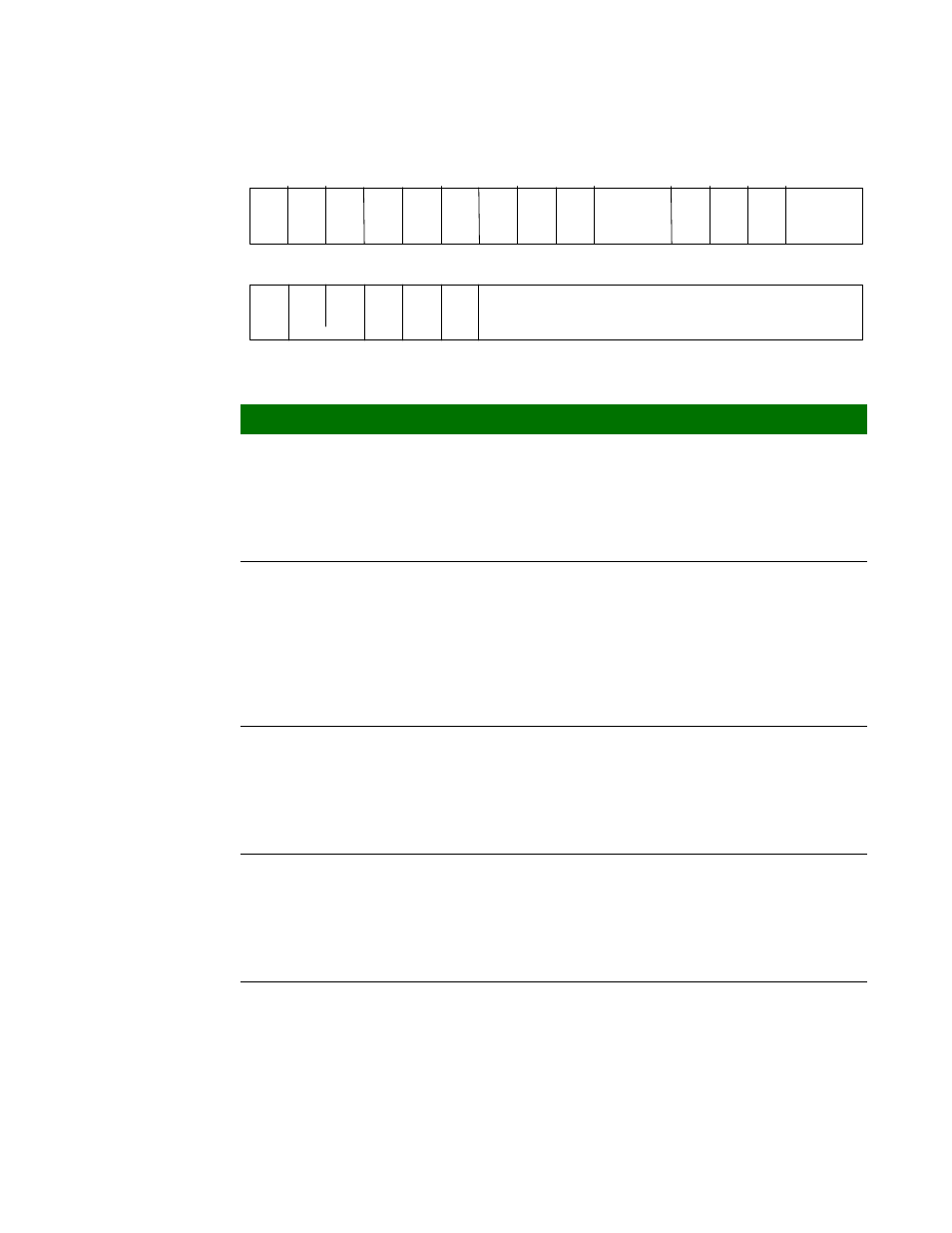

I / O H U B M O D U L E

[Module] Interrupt and FIFO Status register

www.digiembedded.com

373

Register

Register bit

assignment

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

RXN

CIP

RXE

CIP

RXN

RIP

RXC

AIP

RXF

OFIP

TXN

CIP

TXFU

FIP

TXFS

RIP

RX

FIFO

empty

Reserved

MOD

IP

RXP

CIP

RXFS

RIP

RXFS

RIP

RXFS

RIP

RXFS

RIP

RXPB

USY

RX

FIFO

full

TXPB

USY

TX

FIFO

full

TX

FIFO

empty

Bit(s)

Access

Mnemonic

Reset

Description

D31

R/W*

RXNCIP

0x0

Normal completion interrupt pending (RX)

Set when a buffer is closed under normal

conditions. An interrupt is generated when the I bit

is set in the current buffer descriptor.

A normal DMA completion occurs when the

buffer length field expires.

D30

R/W*

RXECIP

0x0

Error completion interrupt pending (RX)

Set when the DMA channel finds either a bad

buffer descriptor or a bad data buffer pointer.

The DMA channel remains in the ERROR state

until the CE bit in the DMA Control register is

cleared and then set again. The DMA channel then

uses the buffer descriptor as set in the index

control field.

D29

R/W*

RXNRIP

0x0

Buffer not ready interrupt pending (RX)

Set when he DMA channel finds a buffer

descriptor with the F bit not set.

The DMA channel remains in the ERROR state

until the CE bit is set in the DMA Control register

is cleared and then set again.

D28

R/W*

RXCAIP

0x0

Channel abort interrupt pending (RX)

Set when the DMA channel finds the channel

abort (CA) bit set.

The DMA controller closes the current buffer

descriptor and remains in the IDLS state until the

CA bit is cleared and the CE bit is set.

D27

R/W*

RXPCIP

0x0

Premature completion interrupt pending

Set when a buffer descriptor is closed by the

peripheral instead of by reaching the buffer length.

The DMA channel continues processing buffer

descriptors