Rx_a buffer descriptor pointer offset register, Register bit assignment – Digi NS9215 User Manual

Page 323

. . . . .

E T H E R N E T C O M M U N I C A T I O N M O D U L E

RX_A Buffer Descriptor Pointer Offset register

www.digiembedded.com

323

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

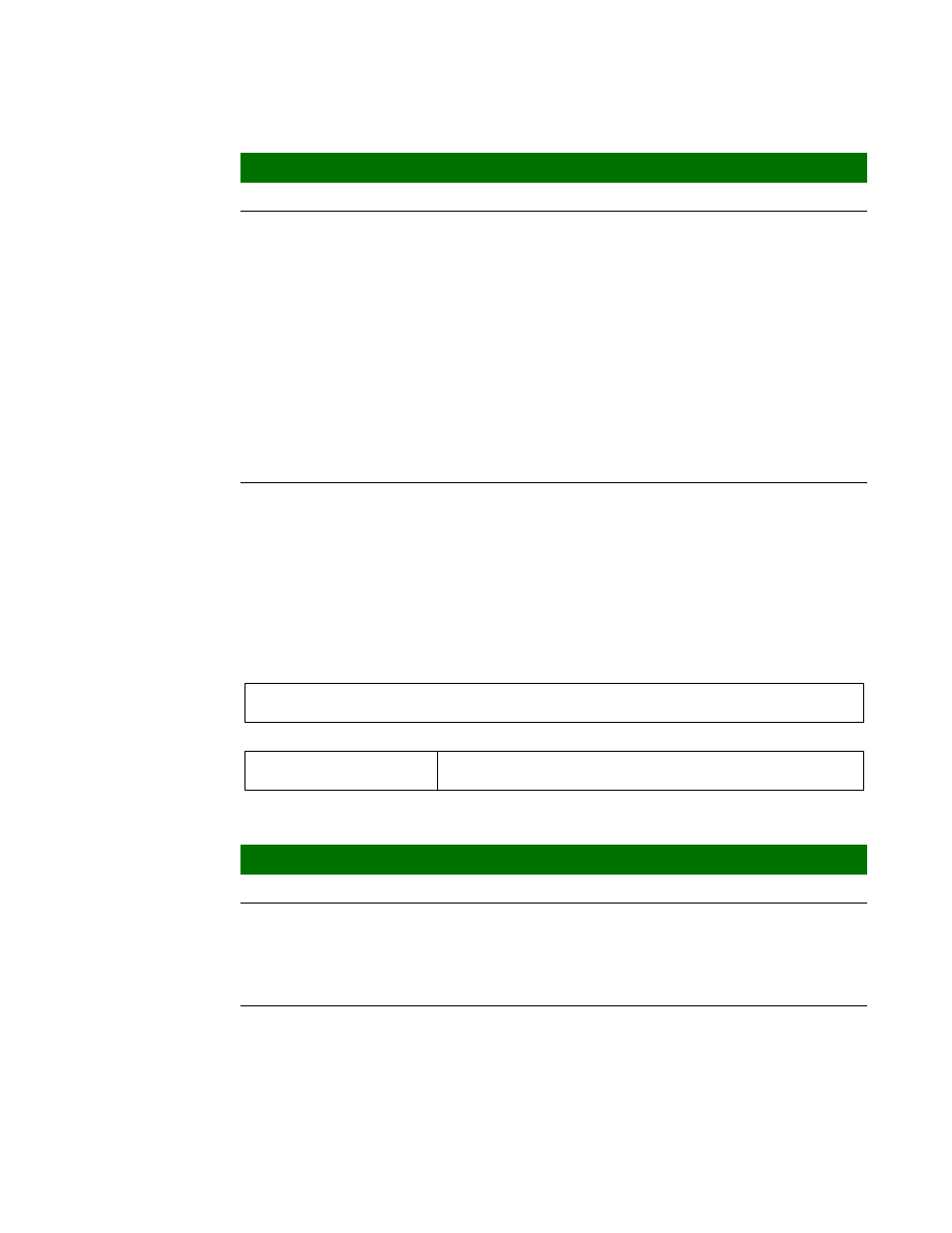

R X _ A B u f f e r D e s c r i p t o r P o i n t e r O f f s e t r e g i s t e r

Address: A060 0A28

Register

Register bit

assignment

Bits

Access

Mnemonic

Reset

Description

D31:08

N/A

Reserved

N/A

N/A

D07:00

R

TXSPTR

0x00

If the TX runs out of frames to send, it sets TXIDLE in the

Ethernet Interrupt Status register and stores the pointer (in

the TX buffer descriptor RAM) to the buffer descriptor

that did not have its F bit set in the TX Stall Buffer

Descriptor Pointer register.

Note:

This pointer is the 8-bit physical address of the

TX buffer descriptor RAM, and points to the

first location of the four-location buffer

descriptor. The byte offset of this buffer

descriptor can be calculated by multiplying this

value by 4.

Note:

Software uses TXSPTR to identify the entry in

the TX buffer descriptor RAM at which the TX

stalled.

Reserved

RXAOFF

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

Bits

Access

Mnemonic

Reset

Description

D31:11

N/A

Reserved

N/A

N/A

D10:00

R

RXAOFF

0x000

Contains an 11-bit byte offset from the start of the pool A

ring. The offset is updated at the end of the RX packet,

and will have the offset to the next buffer descriptor that

will be used. RXAOFF can be used to determine where

the

RX_RD

logic will put the next packet.