Timer 0-9 reload count and compare register – Digi NS9215 User Manual

Page 173

. . . . .

S Y S T E M C O N T R O L M O D U L E

Timer 0-9 Reload Count and Compare register

www.digiembedded.com

173

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

T i m e r 0 - 9 R e l o a d C o u n t a n d C o m p a r e r e g i s t e r

Addresses: A090 0028 / 002C / 0030 / 0034 / 0038 / 003C / 0040 / 0044 / 0048 /

004C

The Timer 0 to 9 Reload Count and Compare register holds the up/down reload and

compare values for timers 0 to 9.

Register

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

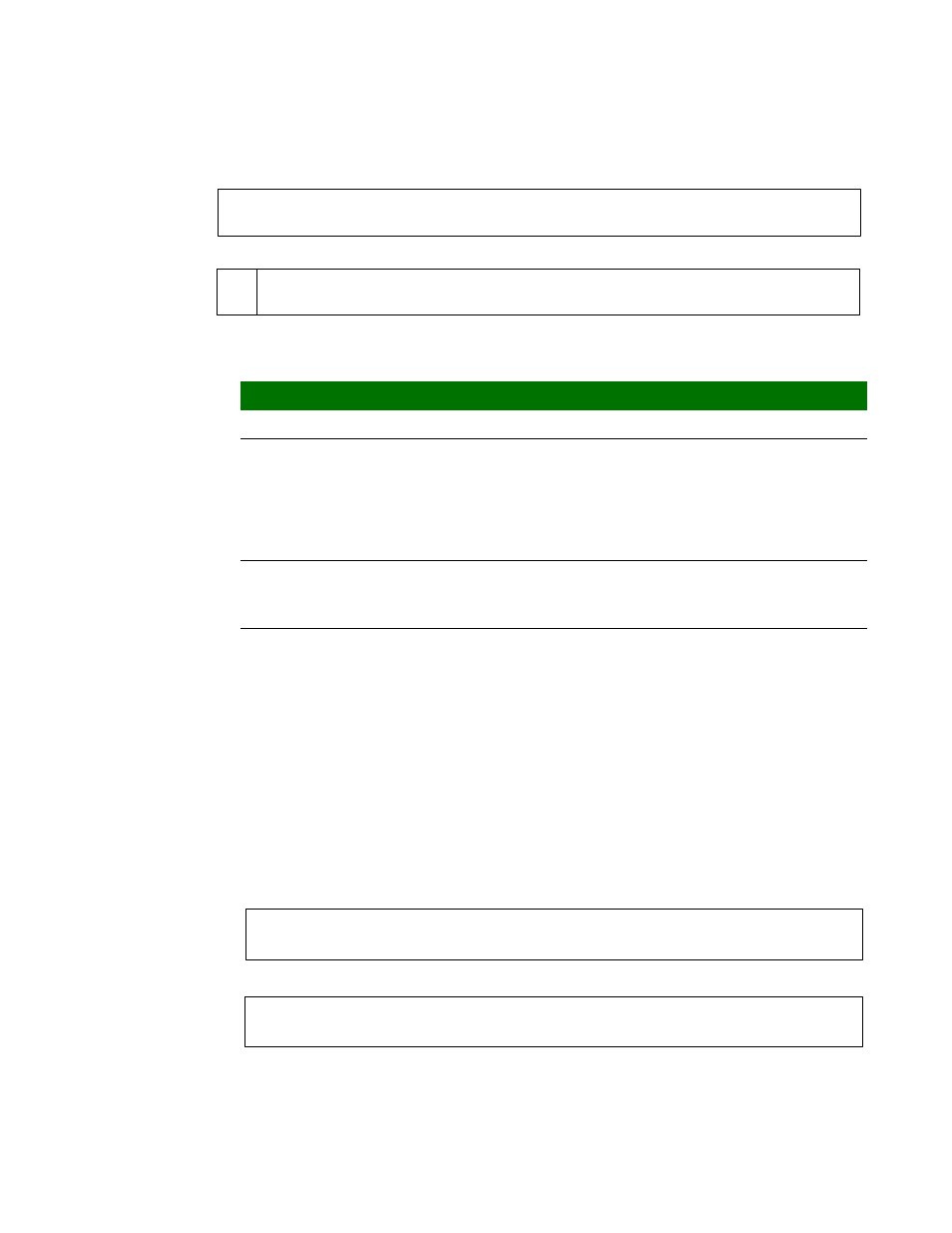

Rel

Dir

Reserved

Rel Step

Bits

Access

Mnemonic

Reset

Description

D31:16

N/A

Reserved

N/A

N/A

D15

R/W

Rel Dir

0x0

Reload step direction

0

Subtract the reload step value from the original

reload register value to increase the overall

period.

1

Add the reload step value to the original reload

register value to decrease the overall period.

D14:00

R/W

Rel Step

0x0

Reload step

This value is either added or subtracted from the

original low register value once each cycle.

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Comp Rel Cnt

Rel 15:0