Spi slave timing diagram – Digi NS9215 User Manual

Page 445

. . . . .

S E R I A L C O N T R O L M O D U L E : S P I

SPI timing characteristics

www.digiembedded.com

445

2

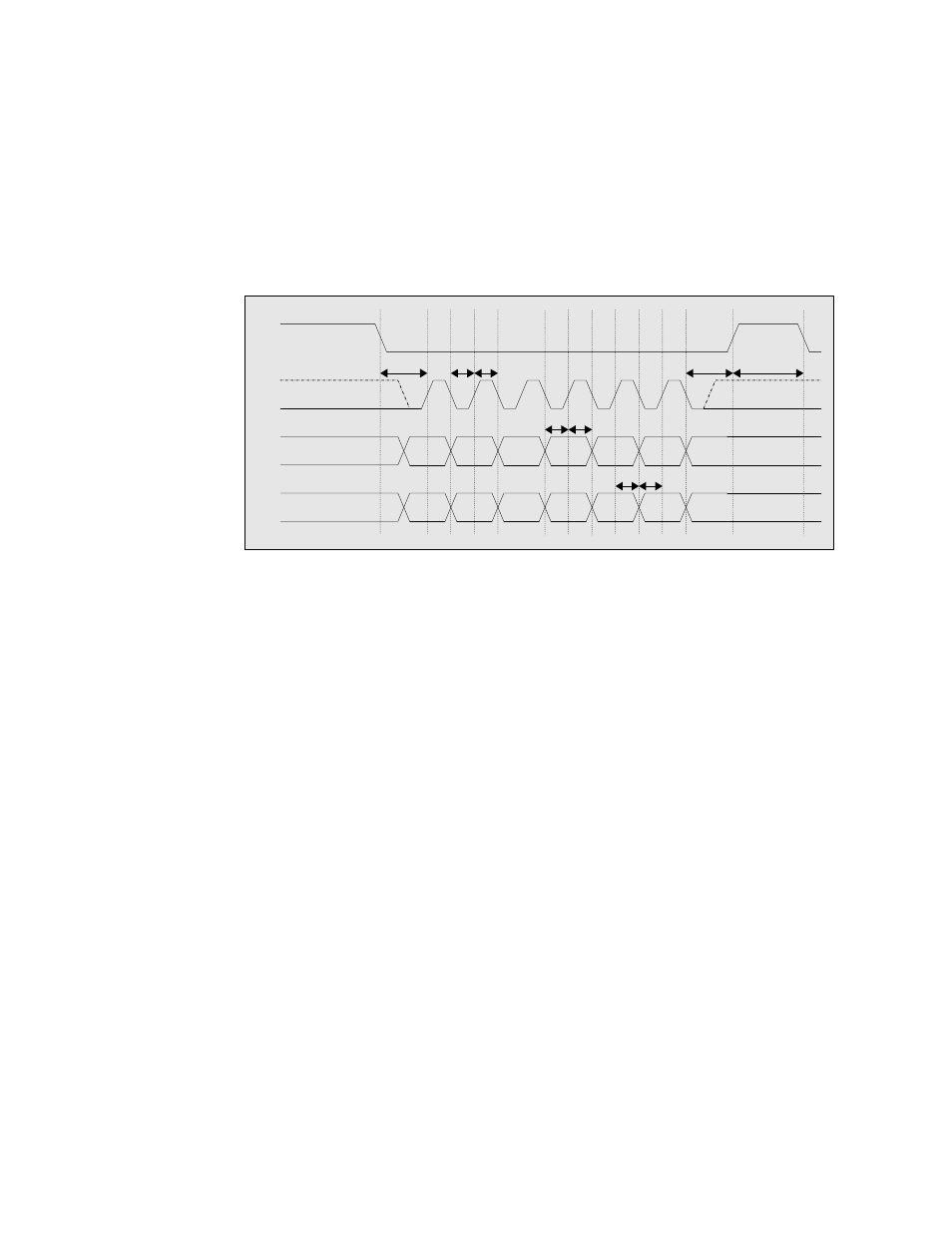

The numbers shown here are for a 7.5 Mhz SPI slave interface clock rate.

3

The numbers shown here are for a 300 Mhz PLL output frequency. This value

must be proportionally increased with a PLL output frequency decrease.

4

This parameter does not depend on any clock frequency.

SPI slave timing

diagram

Mode3

S11

Mode0

CS#

SDI

CLK

SDO

S12 S13

S15

S14

S19

S18

S17

S16