7 additional changes – Motorola DSP96002 User Manual

Page 829

MOTOROLA

47

7 ADDITIONAL CHANGES

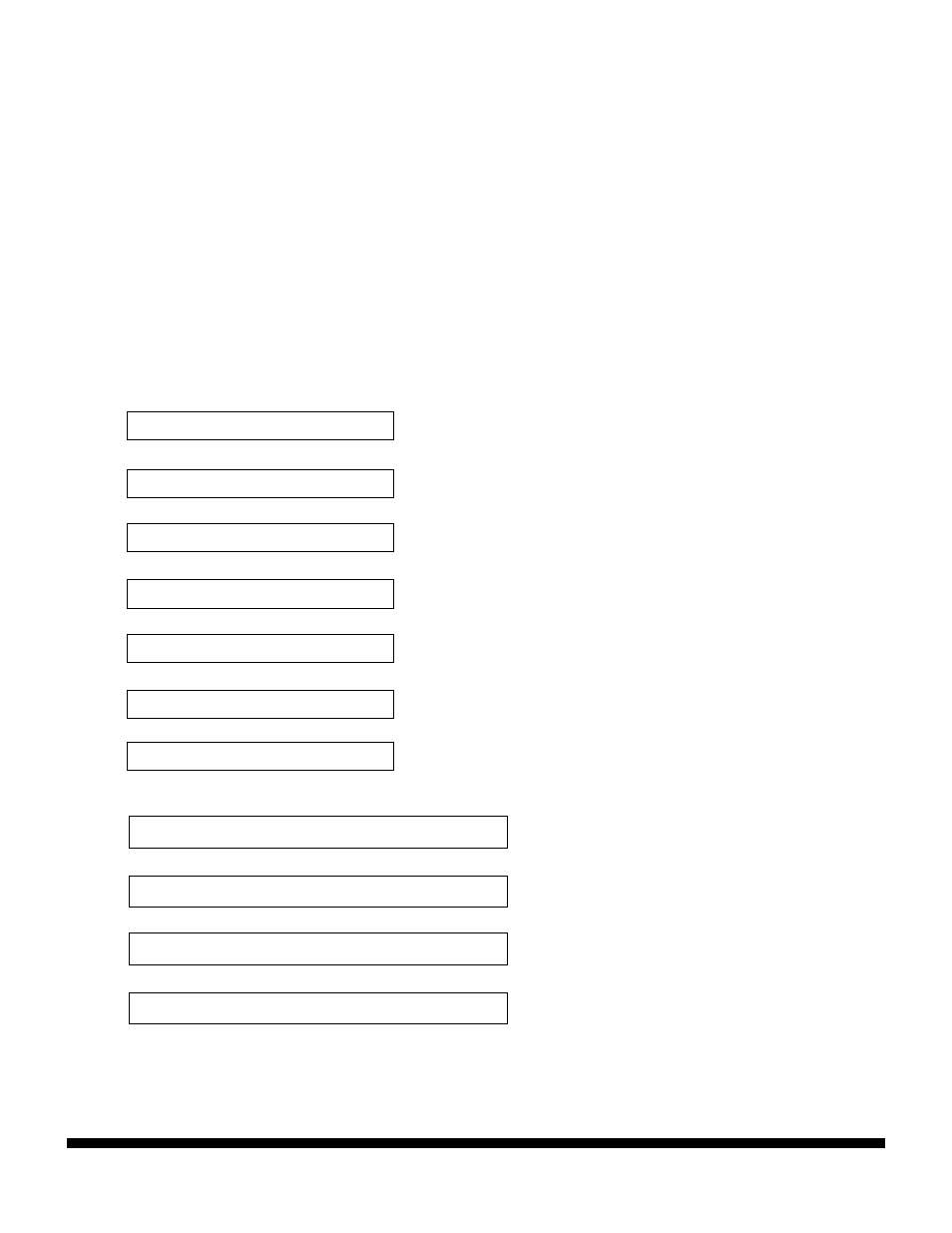

This section presents various other changes to the DSP96002 to support the addition of

the Timer/Event Counter modules. Specifically, two new DMA mask bits (M7 and M8) were

added to the DMA Control/Status Register. Figure 20 and Figure 20 indicate the changed

DMA Controller Programming Models. Table 3 indicates the DMA Request Mask Bits func-

tions. The DMA Controller Programming Model is discussed on Section 7 of the

DSP96002 User’s Manual (DSP96002UM/AD)

This section also presents the X Memory map, interrupt vector addresses, the list of pri-

orities within an IPL, and the interrupt priority register for the DSP96002, all of which have

been changed in support of the timer modules.

DMA Source Modifier Register

DSM0

addr X:$FFFFFFDF

DMA Source Address Register

DSR0

addr X:$FFFFFFDE

DMA Source Offset Register

DSN0

addr X:$FFFFFFDD

DMA Destination Modifier Register

DDM0

addr X:$FFFFFFDB

DMA Destination Address Register

DDR0

addr X:$FFFFFFDA

DMA Destination Offset Register

DDN0

addr X:$FFFFFFD9

DMA Counter

DCO0

addr X:$FFFFFFDC

31

30

29

28

27

26

25

24

DMA Control/Status Register

DCS0

DE

DIE

*

DTD

*

DTM1 DTM0

DMAP

addr X:$FFFFFFD8

23

22

21

20

19

18

17

16

DCP

*

*

*

*

*

*

M8

15

14

13

12

11

10

9

8

M7

M6

M5

M4

M3

M2

M1

M0

7

6

5

4

3

2

1

0

*

*

DSS2

DSS1 DSS0 DDS2

DDS1

DDS0

Figure 20 - DMA Controller Programming Model - Channel 0

31

0