Asr arithmetic shift right asr – Motorola DSP96002 User Manual

Page 217

MOTOROLA

DSP96002 USER’S MANUAL

A - 29

ASR

Arithmetic Shift Right

ASR

Operation:

Assembler Syntax:

ASR D

(move syntax - see the MOVE instruction description.)

ASR S,D

(move syntax - see the MOVE instruction description.)

ASR #shift,D

Description:

Single-bit shift: Arithmetically shift the low portion of the specified operand one bit to the right. The carry

bit receives the LSB shifted out of the low portion of the source operand. The MSB of the operand is held

constant. The result is stored in the low portion of D.

Multi-bit shift: Arithmetically shift the low portion of the specified operand N bits (up to 63 bits) to the right.

The number of bits to shift is determined by the 11-bit unsigned integer located in the 11 LSBs of the high

portion of S or by a 6-bit immediate field in the instruction. The carry bit receives the Nth bit shifted out of

the low portion of the source operand; it is cleared for a shift count of zero. N copies of the MSB of the

operand are shifted into the N MSBs of the destination operand. If more than 32 bits are shifted, copies

of the MSB will be stored in D and the carry bit. The result is stored in the low portion of D.

Input Operand(s) Precision: 32-bit integer.

Output Operand Precision: 32-bit integer.

CCR Condition Codes:

C

- Set if the last bit shifted out of the operand is set. Cleared otherwise. Cleared for a

shift count of zero.

V

- Always cleared.

Z

- Set if result is zero. Cleared otherwise.

N

- Set if result is negative. Cleared otherwise.

I

- Not affected.

LR

- Not affected.

–

R

- Not affected.

A

- Not affected.

ER Status Bits:

Not affected.

IER Flags:

Not affected.

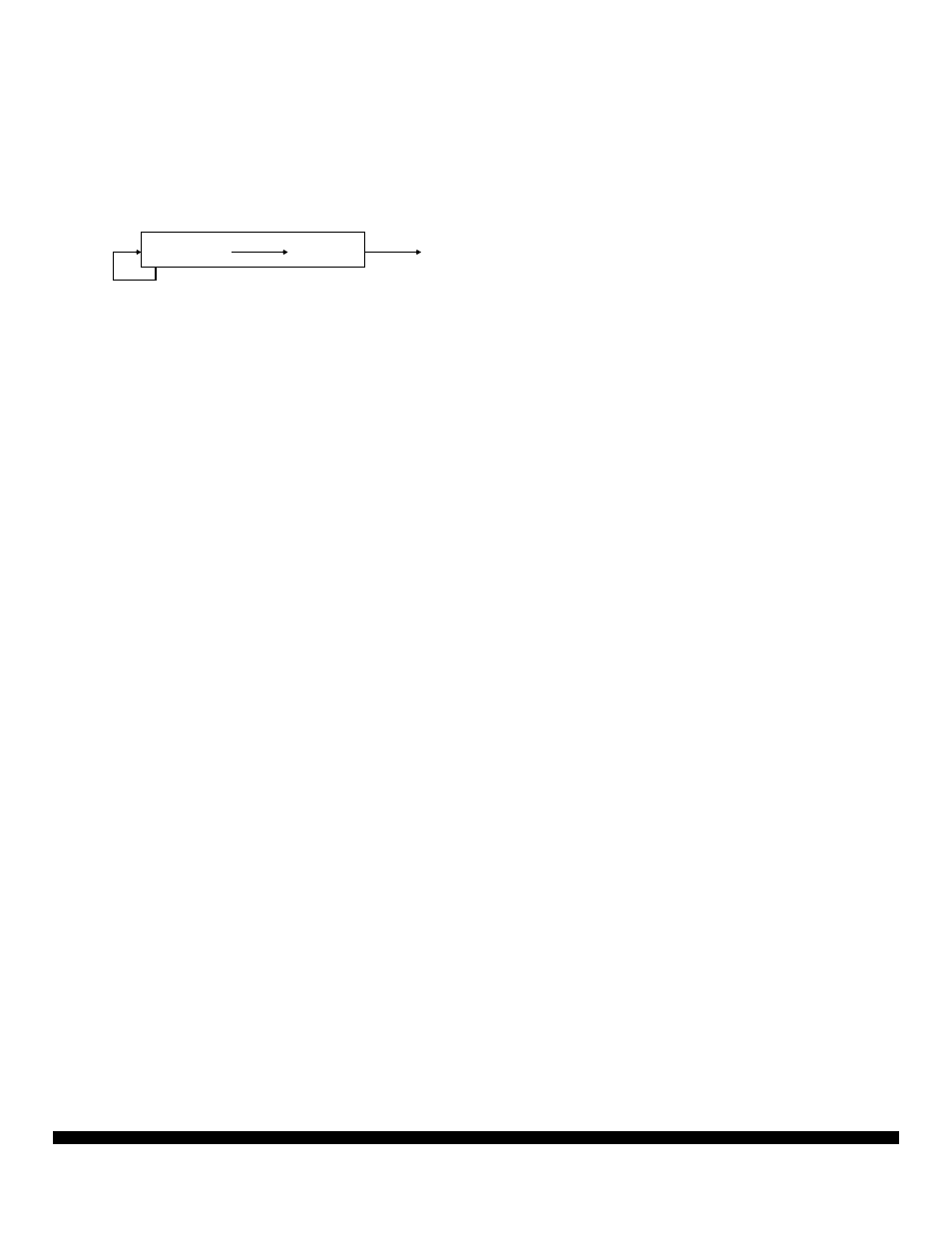

31

0

C

(parallel data bus move)