Motorola DSP96002 User Manual

Page 23

2 - 20

DSP96002 USER’S MANUAL

MOTOROLA

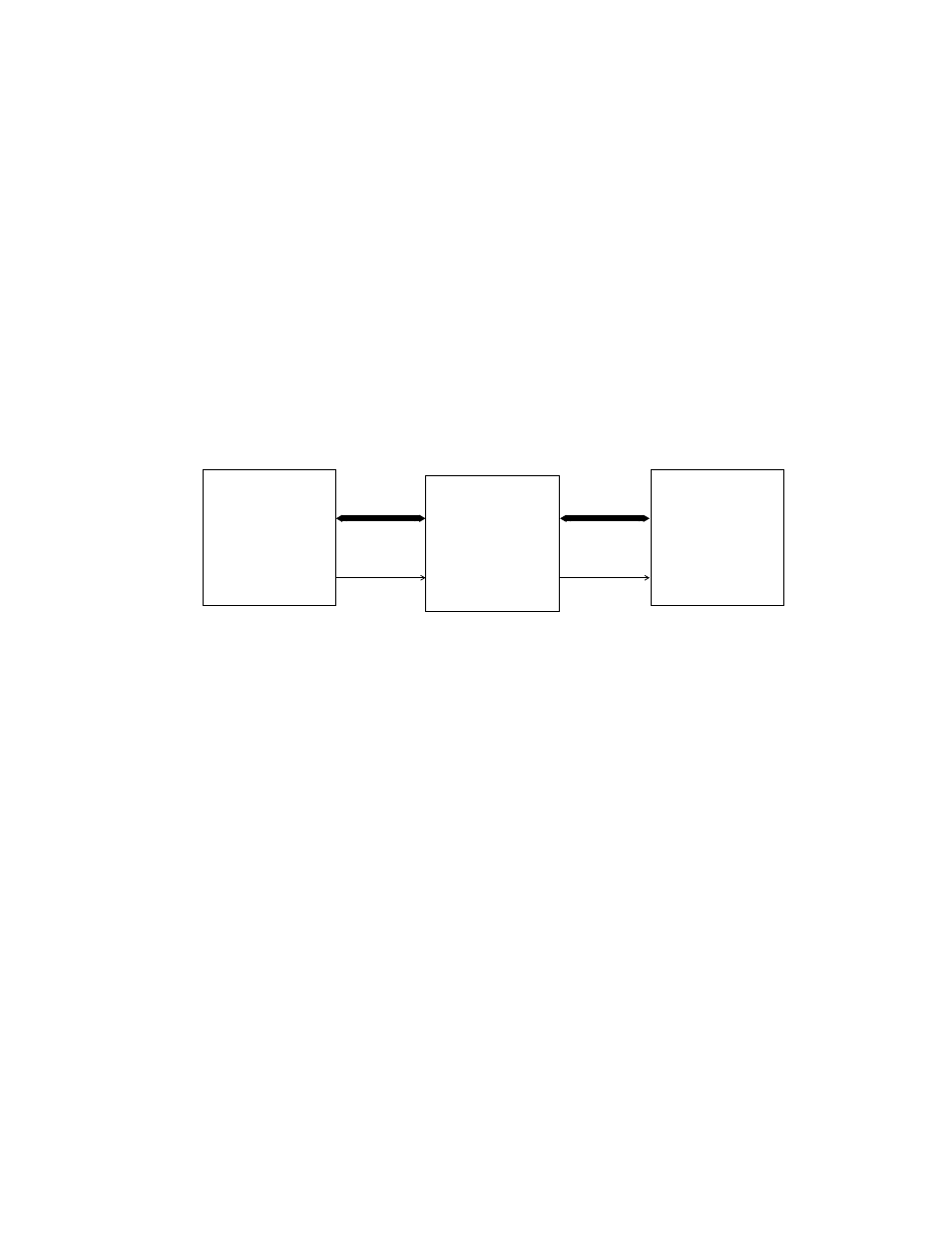

5.16.3.5 Case 5 – Bus Lock during RMW

If the device requesting mastership asserts

—

B

–

R and the arbiter asserts the requesting devices’

—

B

–

G

and

—

B

–

B is deasserted, then the requesting device will assert

—

B

–

A. If a read-modify-write (RMW) in-

struction which accesses external memory is being executed, and the bus arbiter deasserts

—

B

–

G, then

—

B

–

A will remain asserted until the entire RMW instruction completes execution.

—

B

–

A will then be deas-

serted thereby relinquishing the bus. Note that during external RMW instruction execution,

—

B

–

L is assert-

ed. In general, the

—

B

–

L signal can be used to ensure that a multiport memory can only be written by one

master at a time. That is, referring to Figure 2-10,

—

B

–

L can be input from DSP #1to the memory controller

which prevents

—

T

–

A from being asserted by the controller (thereby suspending the memory access by

DSP #2) until DSP #1 completes its RMW access.

5.16.3.6 Case 6 – Bus Park

The device requesting mastership asserts

—

B

–

R; the arbiter asserts the requesting devices’

—

B

–

G and

—

B

–

B is deasserted indicating the bus is not busy – the requesting device will assert

—

B

–

A. When the

requesting device no longer requires the bus it will deassert

—

B

–

R; if the bus arbiter leaves

—

B

–

G assert-

ed because other requests are not pending, then

—

B

–

A will remain asserted. This condition is called bus

parking and eliminates the need for the last bus master to rearbitrate for the bus during its next external

access.

Dual Port

Memory

Controller

DSP96002

#2

#1

RMW

—

B

–

L

—

T

–

A

Figure 2-10. Bus Lock During RMW

DSP96002