Motorola DSP96002 User Manual

Page 120

7 - 34

DSP96002 USER’S MANUAL

MOTOROLA

where this pin is defined as a DMA service request input. When

—

H

–

R is asserted, the master DMA Con-

troller transfers the data word from the external address that selects the RX register in the slave’s HI to a

master memory location. After RX is read (negating

—

H

–

R), the HI may transfer the next data word from

the HI HTX register, setting HTDE and RXDF. Setting RXDF causes

—

H

–

R to be asserted if RREQ is set.

In the slave’s DMA Controller, HTDE is defined as a DMA service request signal. When HTDE is asserted,

the slave’s DMA Controller initiates a data transfer from the slave memory to the HTX register, keeping the

register full for further data transfers.

7.4.20

External DMA Controller to DSP96002 Data Transfers - Examples

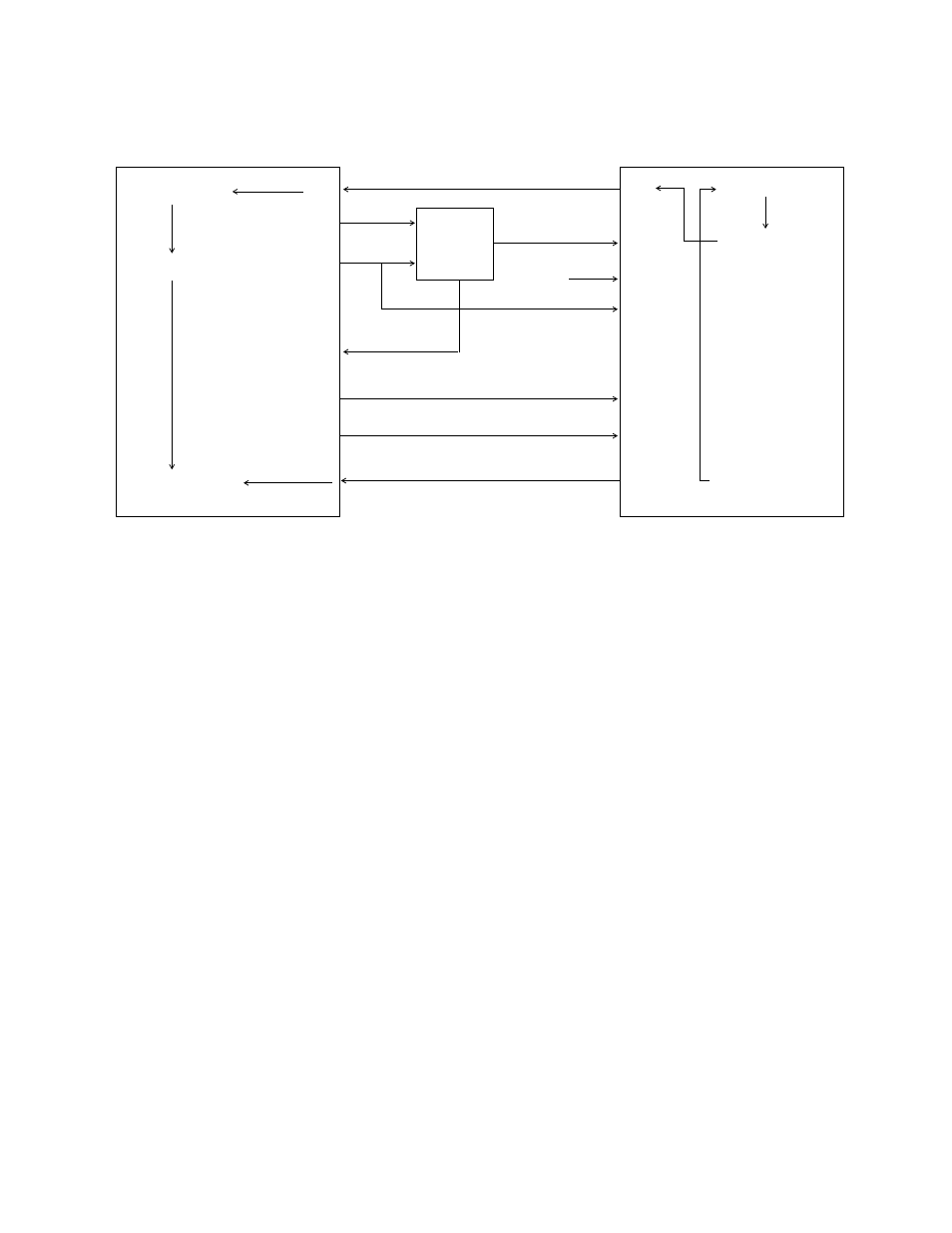

This section presents examples showing the use of the HI and the on-chip DMA Controller for data transfers

between a DSP96002 and an external DMA Controller. The external DMA Controller is the bus master and

the DSP96002 is the bus slave. The external DMA Controller accesses the DSP96002 HI without supplying

an address to select a HI register. Note that the HI is programmed to work in the DMA Mode (DMAE=1).

7.4.20.1

Data Write Using the DSP96002 On-Chip DMA Controller

This example outlines the steps that an external DMA Controller, the bus master, takes to transfer data to

a DSP96002 bus slave, thorough the slave’s HI. The on-chip DMA Controller of the DSP96002 is used to

locally transfer data between the HI and the DSP96002 memory without interfering with core processing.

The TREQ and RREQ bits in the ICS register must be programmed to define the direction of data transfer

as being from the external DMA Controller to the HI (TREQ=1, RREQ=0). The TYEQ bit in the ICS register

DSP96002 Bus Master

DMA Destination

DSP96002 Bus Slave

DMA Source

DMA Request

Bus Master

Read Bus Cycle

into Memory

—

I

—

R

–

Q

S1, S0

A0–A31

—

T

–

A

—

T

–

S

R/

—

W

space

address

data

V

cc

full

slave

select

decode

—

H

–

R

—

H

–

S

—

H

–

A

A2–A5

—

T

–

S

R/

—

W

D0–D31

DMA Request

Memory

→

Host

DMA Transfer

Host Data Empty

Figure 7-18. DSP96002 to DSP96002 Data Read

Receive Data Full

(RXDF=1)

(HTDE=1)