Motorola DSP96002 User Manual

Page 50

MOTOROLA

DSP96002 USER’S MANUAL

4 - 11

31

6

5

4

3

2

1

0

*

UF

SE

P3

P2

P1

P0

are checked. If it is not one, the LC is decremented, and the next instruction is taken from the address at

the top of the system stack; otherwise the PC is incremented, the loop flag is restored (pulled from stack),

the stack is purged, the LA and LC registers are pulled from the stack and restored and instruction execution

continues normally. The LA register is a 32-bit read/write register written into by a DO instruction and is read

by the system stack for stacking the register.

4.10

SYSTEM STACK (SS)

The system stack is a separate internal RAM 15 locations "deep" and divided into two banks: High (SSH)

and Low (SSL) each 32-bits wide. SSH stores the PC or LA contents; SSL stores the LC or SR contents.

The PC and SR registers are pushed on the stack for subroutine calls and long interrupts (see Section 8).

These registers are pulled from the stack for subroutine returns using the RTS instruction and for interrupt

returns that use the RTI instruction. The system stack is also used for storing the address of the beginning

instruction of a hardware program loop as well as the SR, LA and LC register contents just prior to the start

of the loop. This allows nesting of DO loops.

Up to 15 long interrupts, 7 DO loops, or 15 JSRs or combinations of these can be accommodated by the

Stack. Care must be taken when approaching the stack limit. When the Stack limit is exceeded the data to

be stacked will be lost and a non-maskable Stack Error interrupt will occur.

4.11

STACK POINTER (SP)

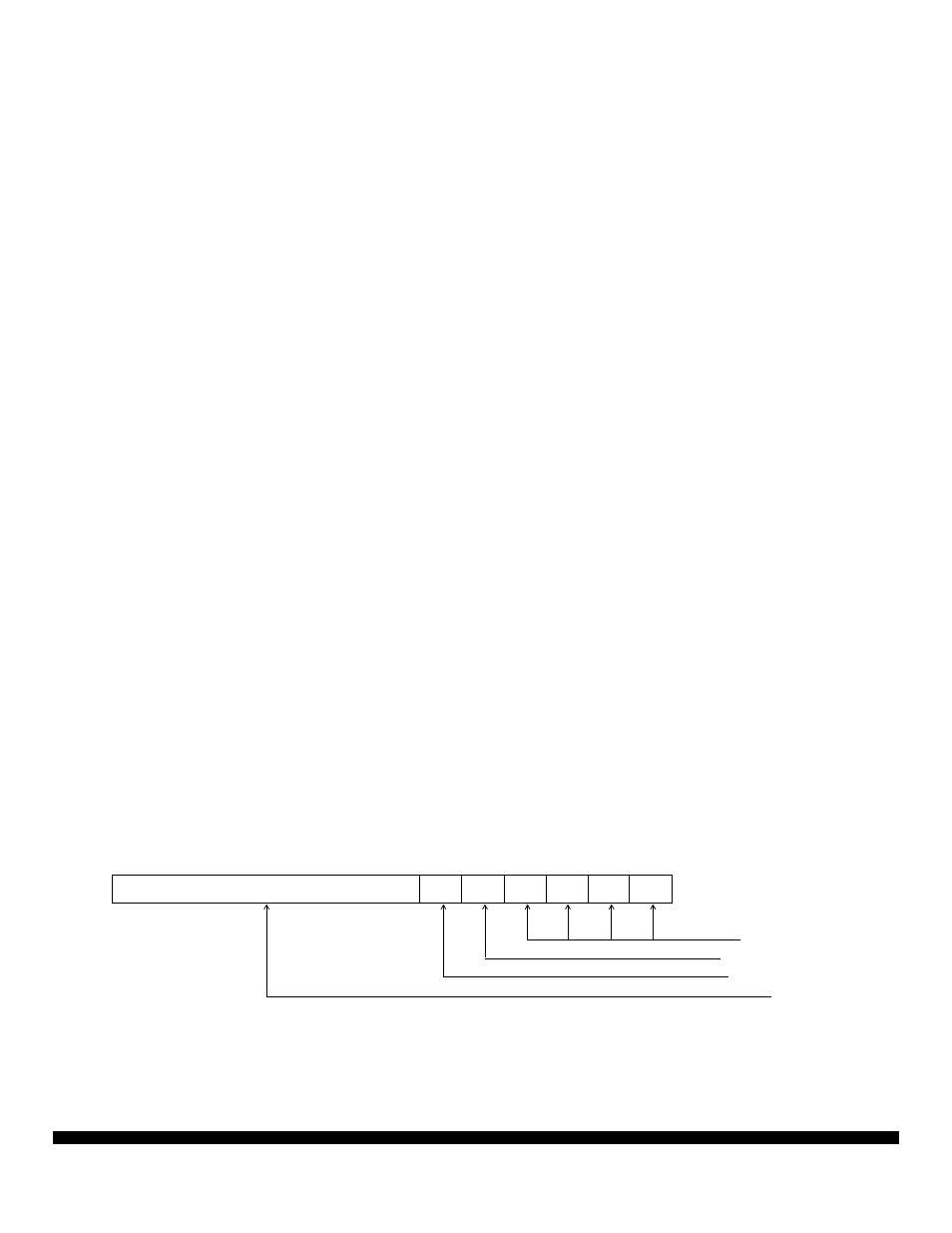

The stack pointer register (SP) is a 32-bit register that indicates the location of the top of the system stack

and the status of the stack (underflow and overflow error conditions). The stack pointer is referenced implic-

itly by some instructions (DO, ENDDO, REP, JSR, RTI, etc.) or directly by the MOVEC, MOVEI, MOVEM,

MOVEP and MOVES instructions. The stack pointer register format is shown in Figure 4-4. Note that the

stack pointer register is implemented as a six bit counter which addresses (selects) a fifteen location stack

with its four least significant bits. The possible stack values are shown in Figure 4-5 and are described be-

low.

4.11.1

Stack Pointer (SP) Bits 0,1,2,3

The stack pointer (SP) points to the last used place on the stack. Immediately after hardware reset these

bits are cleared (SP=0), indicating that the stack is empty.

Stack Pointer

Stack Error Flag

Underflow Flag

Reserved

Figure 4-4. Stack Pointer Format