Operating modes and program memory maps – Motorola DSP96002 User Manual

Page 157

MOTOROLA

DSP96002 USER’S MANUAL

9 - 1

SECTION 9

CHIP OPERATING MODES AND MEMORY MAPS

9.1

OPERATING MODES AND PROGRAM MEMORY MAPS

The operating mode bits MA, MB, and MC in the OMR register determine the bus expansion mode for pro-

gram memory and the startup procedure when the DSP96002 leaves the RESET state. The Data ROM

Enable bit DE in the OMR determines the bus expansion mode for the data memories.

The MODA, MODB, and MODC pins are used to load MA, MB and MC with the initial operating mode of

the DSP96002. These pins are sampled as the DSP96002 leaves the RESET state. These pins do not

affect the operating mode after that time and are available for other functions. Chip operating modes are

programmable by writing the operating mode bits MA, MB and MC in the operating mode register. Refer

to Section 4.12 for a description of the operating mode register OMR. Figure 9-1 shows the mode assign-

ments.

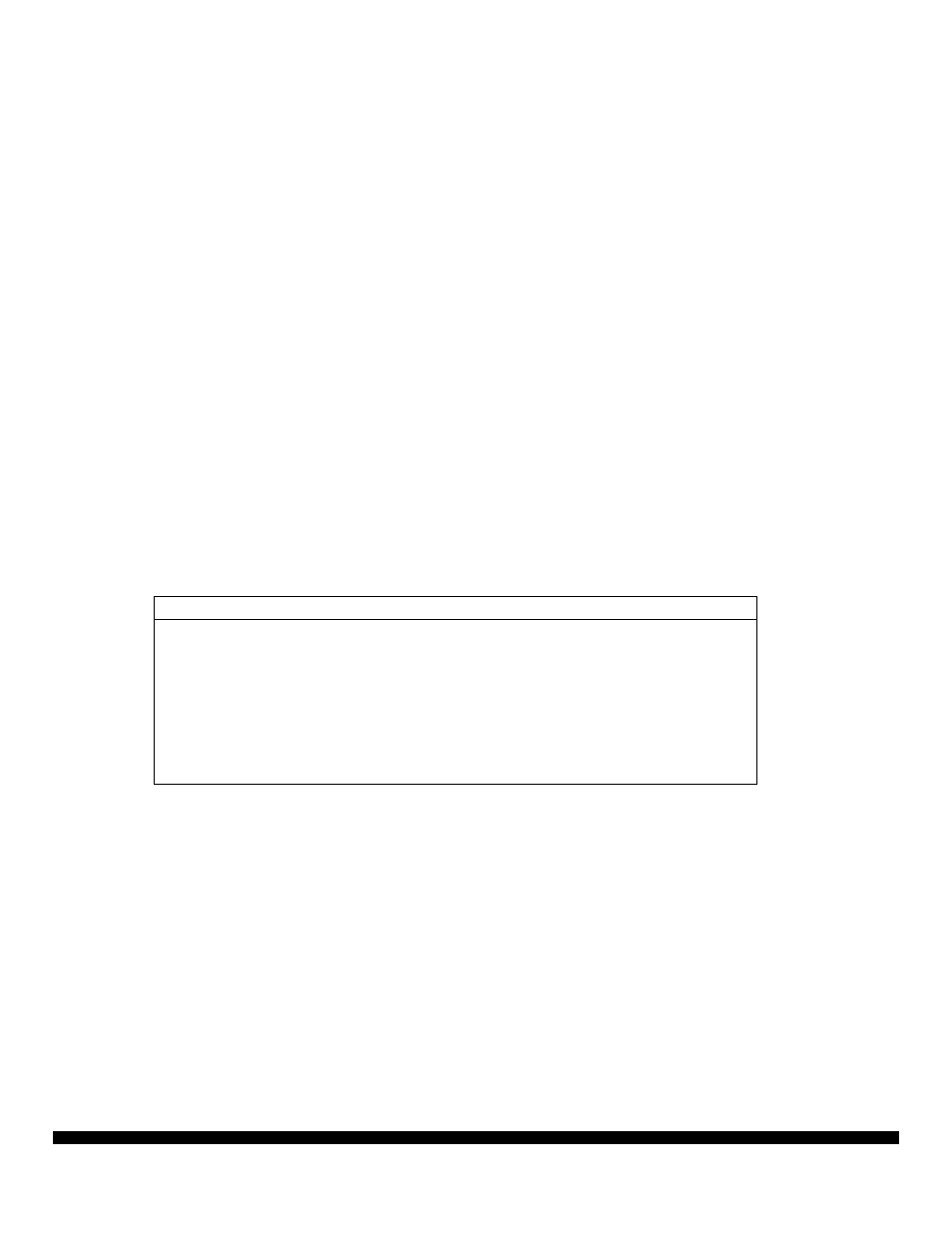

Mode MC MB MA DSP96002 Initial Chip Operating Mode

0 0 0 0 PRAM enabled, Reset at $FFFFFFFE (Port A)

1 0 0 1 PRAM enabled, Reset at $FFFFFFFE (Port B)

2 0 1 0 PRAM disabled, Reset at $00000000 (Port A)

3 0 1 1 PRAM disabled, Reset at $00000000 (Port B)

4 1 0 0 Bootstrap from byte-wide (bits D7-D0)

external memory at $FFFF0000 (Port A)

5 1 0 1 Bootstrap from byte-wide (bits D7-D0)

external memory at $FFFF0000 (Port B)

6 1 1 0 Bootstrap thru the Host Interface (Port A)

7 1 1 1 Bootstrap thru the Host Interface (Port B)

Figure 9-1. DSP96002 Initial Chip Operating Mode Summary

There are eight chip operating modes divided in two groups:

•

Non-bootstrap modes - these modes are used to access program memories that are already

programmed.

•

Bootstrap modes - these modes are used to load the internal program memory implemented

in RAM. After loading the internal program memory, the DSP96002 switches to Mode 0 or 1

but begins program execution at the address located at the on-chip program memory address

$00000000.

9.1.1 Mode 0 (Internal PRAM enabled, Reset at $FFFFFFFE, Port A)

In mode 0, the internal program memory occupies the lower portion of the program memory space. Ad-

dresses higher than the highest internal program memory location are directed to external program mem-

ory. The address of the hardware reset vector is $FFFFFFFE, located in the Port A external program mem-

ory space. The program memory map for this mode is shown in Figure 9-2.