Motorola DSP96002 User Manual

Page 122

7 - 36

DSP96002 USER’S MANUAL

MOTOROLA

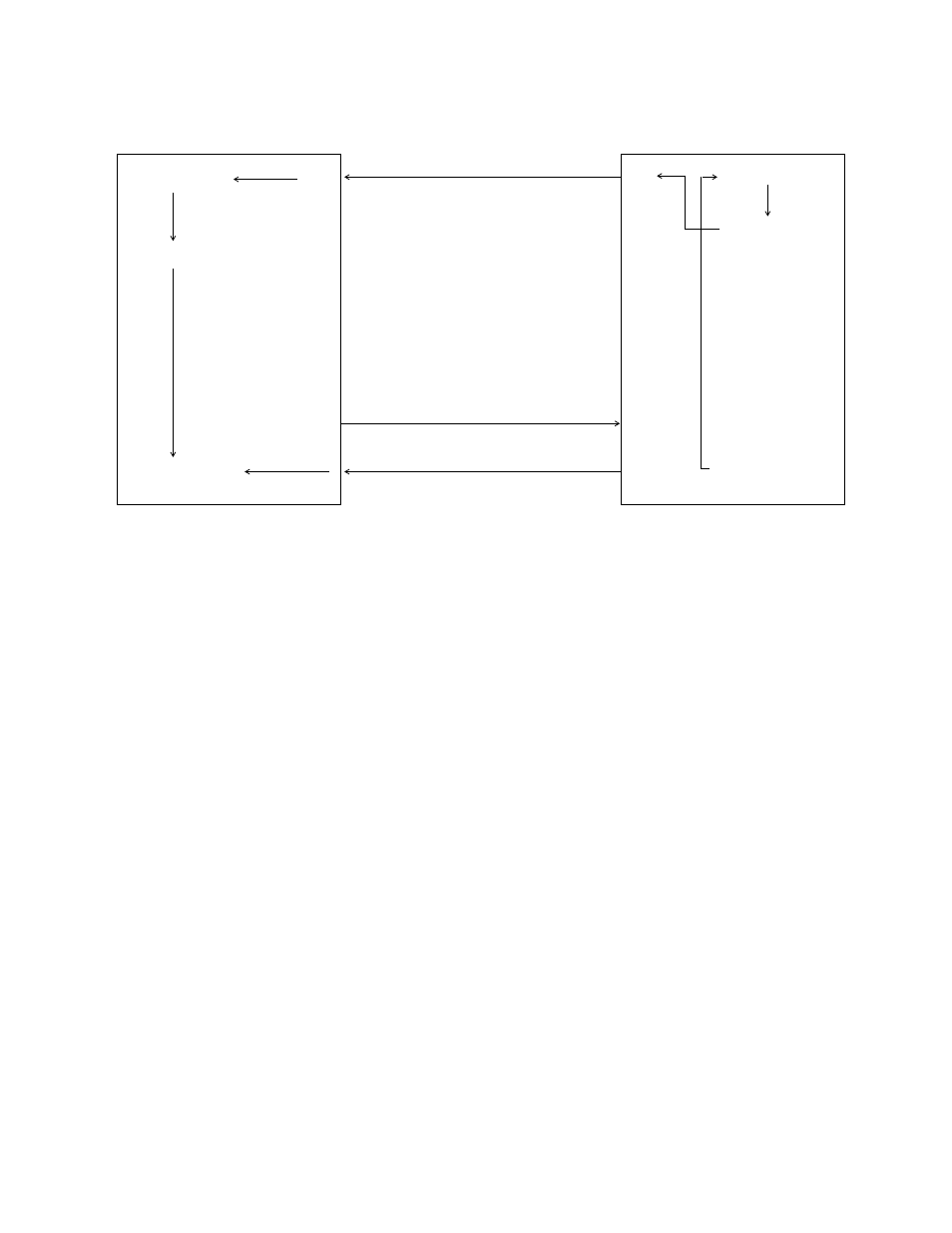

A data read transfer is initiated when the slave’s

—

H

–

R signal is asserted, indicating that its HI RX register

is full and the data is ready to be read by the external DMA Controller.

—

H

–

R is connected to a

—

R

—

E

–

Q

pin in the master which is a DMA service request input. When

—

H

–

R is asserted, the external DMA Con-

troller transfers the data word from the RX register in the slave’s HI to a memory location. The RX register

is read by asserting

—

H

–

A and TREQ=0 and RREQ=1. After RX is read (negating

—

H

–

R), the HI may

transfer the next data word from the HI HTX register, setting HTDE and RXDF. Setting RXDF causes

—

H

–

R to be asserted since RREQ is set. In the slave’s on-chip DMA Controller, HTDE is defined as a DMA ser-

vice request signal. When HTDE is asserted, the slave’s on-chip DMA Controller initiates a data transfer

from the slave memory to the HTX register, keeping the register full for further data transfers.

7.4.21

HI Performance Analysis and Programming Examples

The following host programming examples show the software needed to support Master-Slave transfers be-

tween two DSP96002s. Master processor load, the minimal transfer cycle, and the overhead are estimated.

These estimates can vary depending on the addressing mode. In most cases the fastest addressing mode

possible was used. Also, it was assumed that the master processor did not loose the bus in the middle of

host activity. The HI registers are accessed by the host processor with 0 wait states.

External DMA Controller

Bus Master

DSP96002

Bus Slave

DMA Request

Bus Master

Read Bus Cycle

into Memory

—

R

—

E

–

Q

data

full

—

H

–

R

—

H

–

A

D0–D31

DMA Request

Memory

→

Host

DMA Transfer

Host Data Empty

—

A

—

C

–

K

Figure 7-20. DSP96002 to External DMA Data Read

(HTDE=1)

Receive Data Full

(RXDF=1)