Motorola DSP96002 User Manual

Page 52

MOTOROLA

DSP96002 USER’S MANUAL

4 - 13

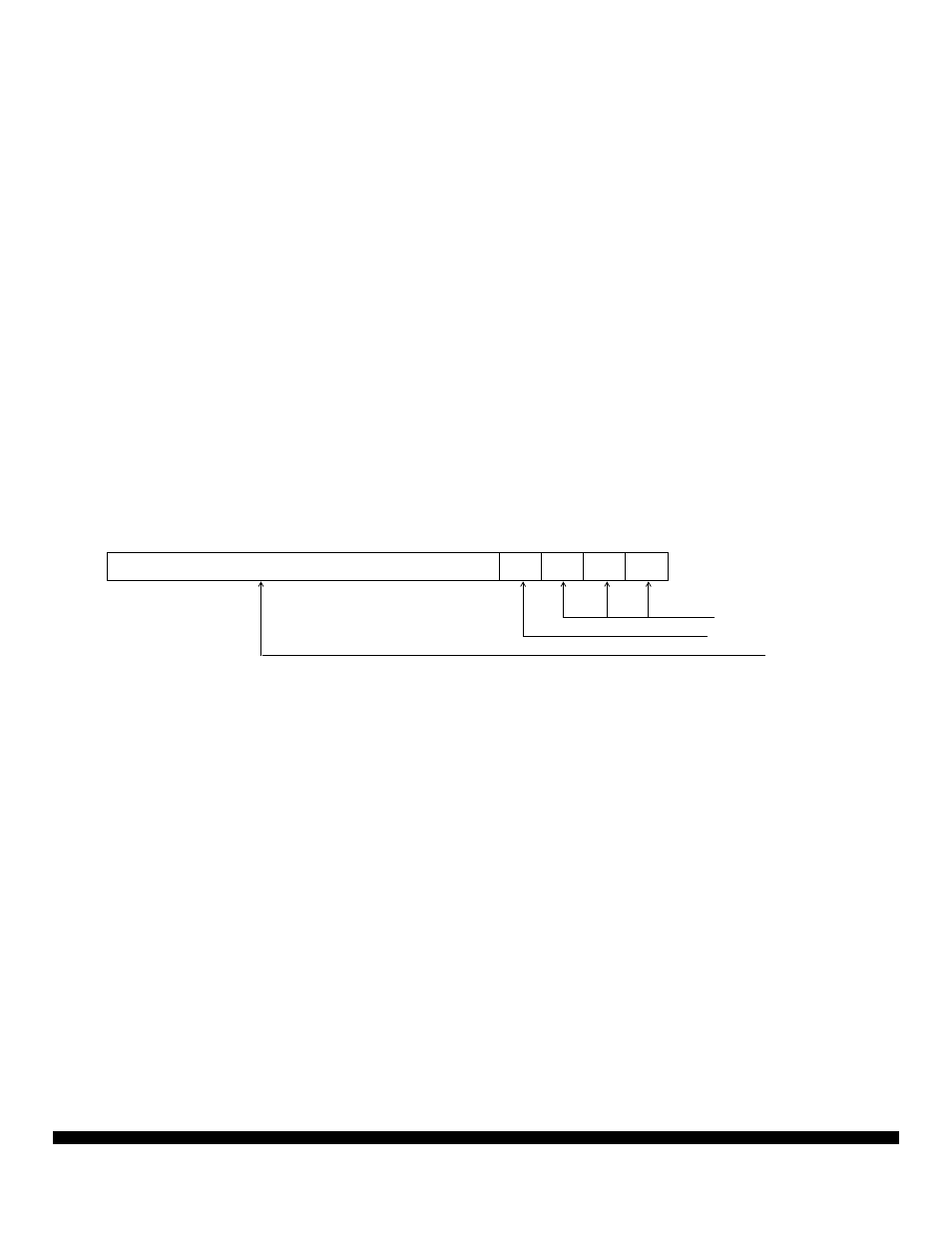

Figure 4-6. Operating Mode Register Format

4.11.3

Underflow flag (UF) Bit 5

The Underflow flag (UF) is set when a stack underflow occurs. The UF flag is cleared when a stack overflow

occurs. While the SE flag remains set, the UF flag does not change with Stack Pointer operations caused

by instructions that refer implicitly to the Stack Pointer such as RTI, RTS, DO, ENDDO, JSR, etc. The UF

flag is cleared by hardware reset (see Figure 4-5). Implicit stack pointer operations that do not produce a

stack error (i.e. do not set SE) will always clear UF as long as SE is not set.

4.11.4

Unimplemented Stack Pointer Register bits (Bits 6-31)

Any unimplemented stack pointer register bits are reserved for future expansion and read as zero during

DSP96002 read operations. They should be written with zero for future compatibility.

4.12

OPERATING MODE REGISTER (OMR)

The operating mode register (OMR) is a 32-bit register which defines the current chip operating mode of the

processor. The OMR bits are only affected by processor reset and by instructions which directly reference

the OMR.

The operating mode register format is shown in Figure 4-6 and is described below.

4.12.1

Chip Operating Mode (Bits 0,1,2)

The operating mode bits MA, MB and MC determine if the internal program RAM is enabled and the startup

procedure when the chip leaves the RESET state. These bits are loaded from the external Mode Select pins

MODC, MODB and MODA respectively when the

—

R

—

E

—

S

—

E

–

T pin is negated. After the DSP96002

leaves the RESET state, MC, MB and MA may be changed under program control. See Section 9 for more

details on the chip operating modes.

4.12.2

Data ROM Enable (Bit 3)

The Data ROM Enable (DE) bit enables the two on-chip 512x32 Data ROMs located at address $00000400

to $000007FF in the X and Y memory spaces. When DE is cleared, the $00000200 to $000007FF space is

part of the external X and Y data spaces and the on-chip Data ROMs are disabled (see the DSP96002 data

memory maps in Section 9.2 for additional details).

4.12.3

Reserved Operating Mode Register (Bits 4-31)

These operating mode register bits are reserved for future expansion and will read as zero during

DSP96002 read operations. They should be written with zero for future compatibility.

31

4

3

2

1

0

Operating Mode

Data Rom Enable

Reserved

*

DE

MC

MB

MA