Motorola DSP96002 User Manual

Page 760

D-8

DSP96002 USER’S MANUAL

MOTOROLA

register file consisting of 10 96-bit registers for storage of floating-point numbers is available for

that purpose. An automatic conversion unit converts the floating point storage format in memory

to the internal DP format when moving operands and/or results from/to memory.

2.

Multiply unit: A full IEEE floating-point multiply unit, delivering either a SP or SEP result in one

instruction cycle.

3.

Adder/Subtracter unit: A full IEEE floating-point adder/subtracter unit, which can deliver the

sum as well as the difference of two operands in the same instruction cycle, to either SP or SEP.

4.

Special function unit: A special function unit provides various logic functions, as well as support

for divide and square root in terms of an initial seed for a fast convergent divide and square root

algorithm.

5.

Controller and arbitrator: A controller/arbitrator supplies all of the control signals necessary for

the operation of the data ALU.

The data ALU uses the SEP format for all of its operations: the results are automatically rounded to either

SP or SEP. All of the rounding modes specified by the IEEE standard are supported. These rounding modes

are:

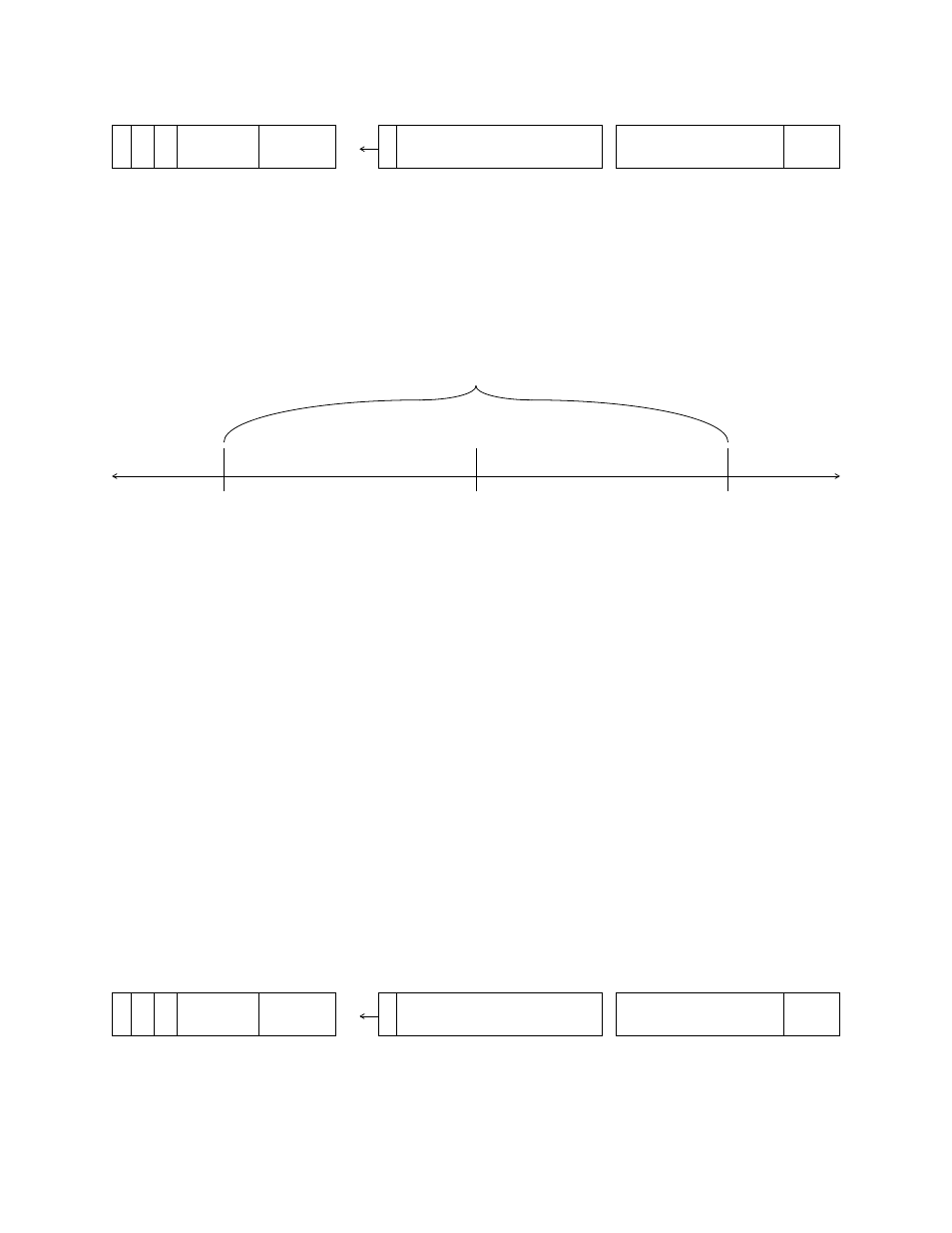

Figure D-5. DP Format in the Data ALU

95 94 93 92

75 74

64

63 62

32

31

11 10

0

S U V

O

E

0

Fraction (MSBs)

Fraction (LSBs)

i

Dn.h

Dn.m

Dn.l

S : sign

U : single precision unnormalized tag

V : double precision unnormalized

i : explicit integer

Tiny SP Numbers between

±

2

Emin

-1.0

Ч

2

-126

0

+1.0

Ч

2

-126

Figure D-6. Tiny Numbers

Figure D-7. SEP Format in the Data ALU

95 94 93 92

75 74

64

63 62

32 31

11 10

0

S U V

O

E

0

Fraction

0

i

Dn.h

Dn.m

Dn.l