Section 5 introduces, 5 once enhancements – Motorola DSP96002 User Manual

Page 803

MOTOROLA

21

5 OnCE ENHANCEMENTS

The OnCE has been enhanced to provide the user with fully non-intrusive system debug

capability when the processor is in cache mode. When the processor is in debug mode,

the OnCE offers the ability to observe the cache status, such as which memory sectors

are currently mapped into cache sectors, which cache sectors are locked, and which

cache sector is the least recently used by reading the tag registers contents, lock bits, and

LRU bits serially.

After the user has determined which memory sectors are in the cache, it is still necessary

to find out which words in each sector are actually valid. Performing a loop for every sector

that accesses the corresponding addresses using MOVEM instruction and testing a status

bit that indicates HIT/MISS will make the determination, which shows again that MOVEM

does not effect the cache status in any way.

5.1

Change to OnCE Status and Control Register (OSCR)

The OnCE status and control register has been changed to support cache mode debug

with the addition of the read-only cache hit (HIT) at bit 20. Bit 20 is set when a cache hit

has occurred when the processor is in cache mode and in debug mode. When the proces-

sor is in PRAM mode, bit 20 will read as zero. Hardware reset clears the HIT bit.

5.2

Change to Register Select Bits (RS4-RS0) of the OnCE Command Format

The Register Select Bits (RS4-RS0) now support a new register address destination to

accommodate writes to the tags buffer. The RS4-RS0 configuration 10010 refers to the

tags buffer (8 tags + locks/lru).

The configuration was previously noted as the Program Address Bus Latch for Decode

(OPABD) in the table on page 10-17 of the DSP96002 User’s Manual (DSP96002UM/AD).

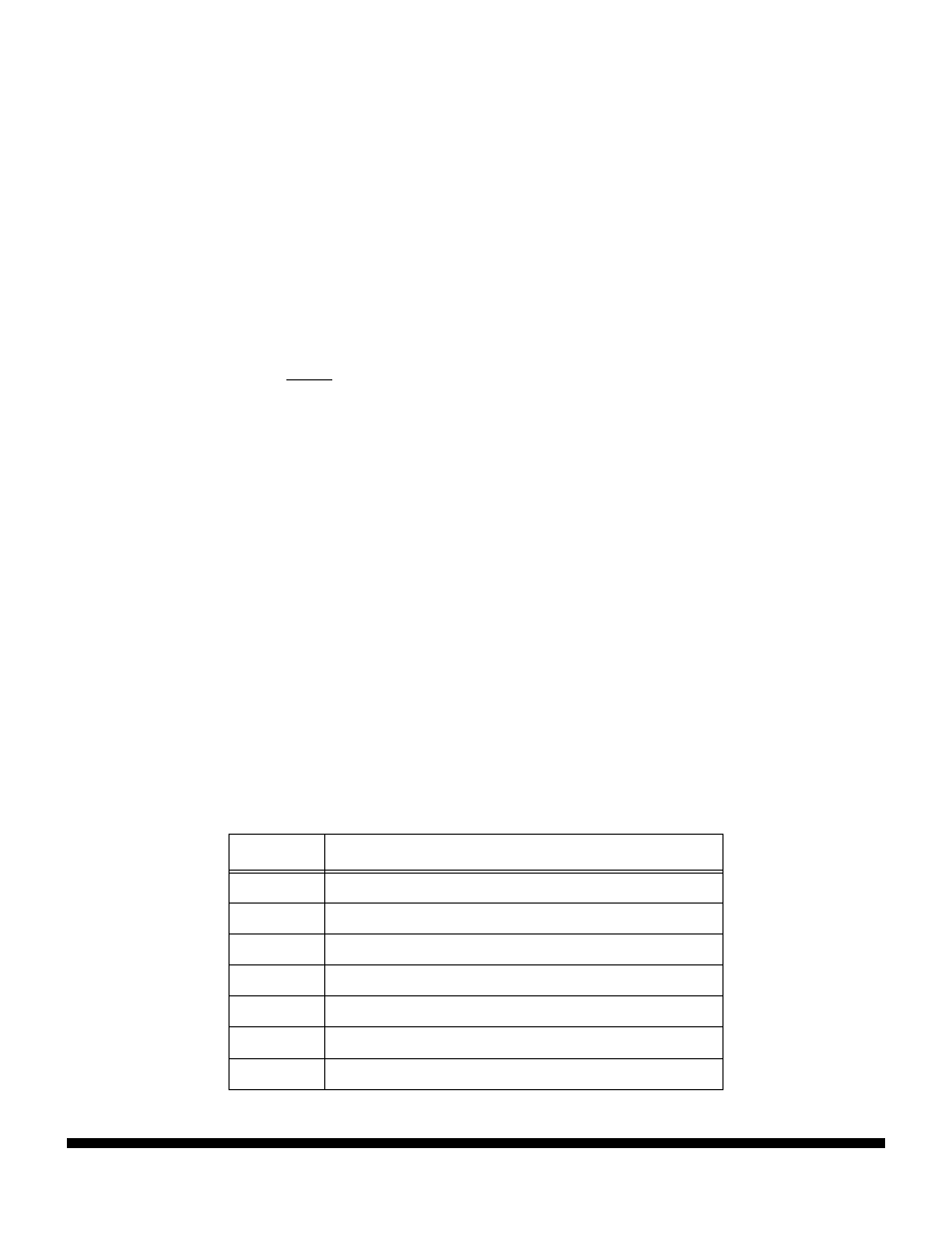

The following table replaces the table currently in the manual.

Table 1 Register Select Bits 4-0 (RS4-RS0)

RS4-RS0

Register Selected

00000

Debug Status/Control (OSCR)

00001

Breakpoint Counter Program (OPBC)

00010

Breakpoint Counter Data (ODBC)

00011

Trace Counter (OTC)

00100

Breakpoint Data Memory Higher-Equal (ODULR)

00101

Breakpoint Data Memory Lower-Equal (ODLLR)

00110

Breakpoint Program Memory Higher-Equal (OPULR)