Motorola DSP96002 User Manual

Page 128

7 - 42

DSP96002 USER’S MANUAL

MOTOROLA

4.

The host processor polls the ICS register until HMRC is cleared and then reads the data D from

the RX register.

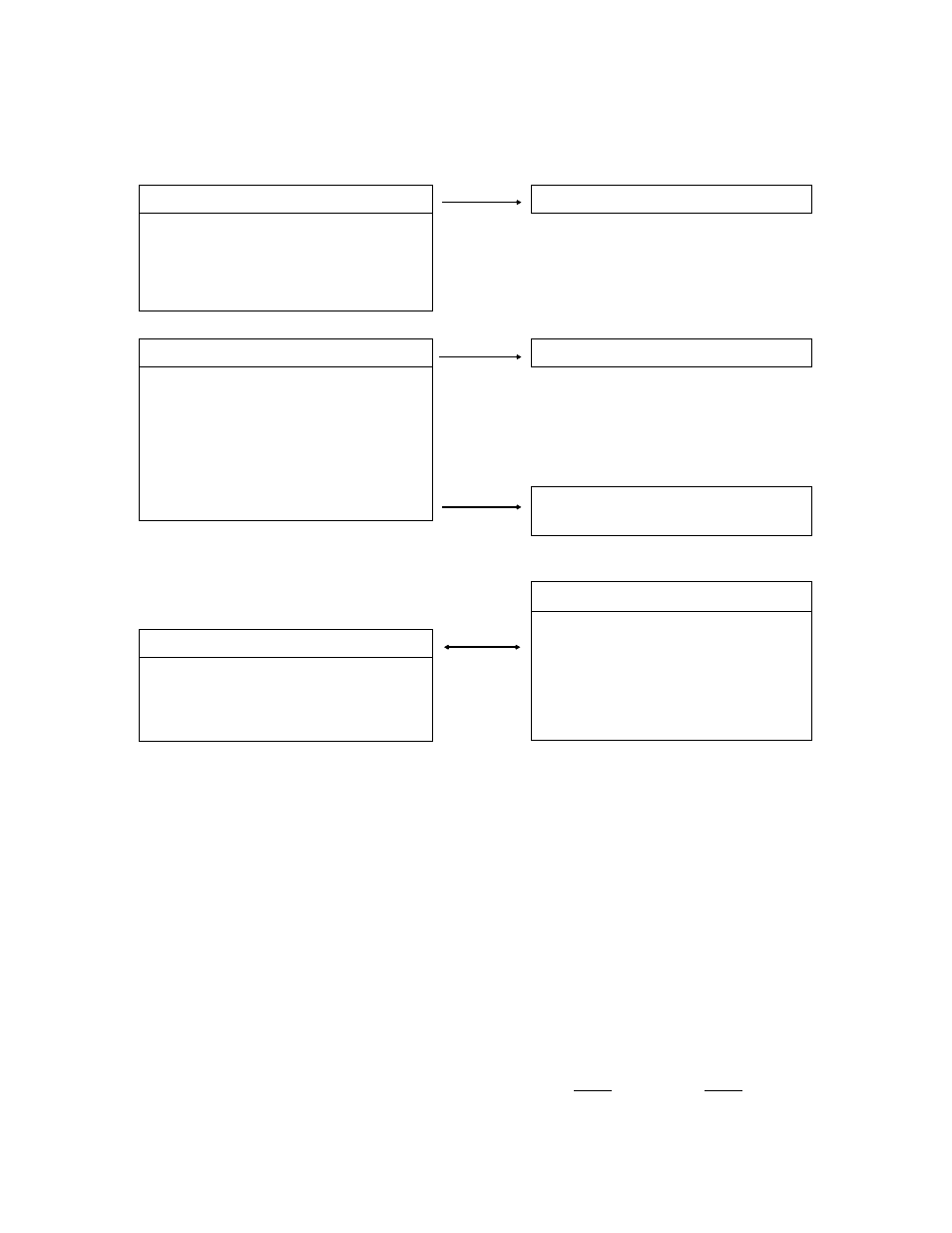

Figure 7-23 shows a flowchart for X Memory Read.

Following is the code executed by the master processor. The R3 register contains the address needed for

selecting the "TX register write and X Memory Read interrupt" host function in the slave HI, as defined in

Figure 7-12. The R4 register contains the address needed for reading the ICS register of the slave HI. The

R1 register contains the target X memory address. The R2 register contains the address needed for reading

the RX register of the slave HI. The required data word is finally stored in D0.s. The master executes the

following instructions:

clock

words cycles

_LOOP1 JCLR #TXDE,X:(R4),_LOOP1 2 6

MOVE R1,X:(R3) 1 2

_LOOP2 JCLR #HMRC,X:(R4),_LOOP2 2 6

MOVE X:(R2),D0.S 1 2

6 16

96K MASTER PROCESSOR 96K SLAVE PROCESSOR

Semaphore Control Semaphore Register (SEM)

1.Set Semaphore in slave’s

Semaphore Register using

BSET Instruction.

2.If Semaphore was set before

repeat step 1 else continue

X Memory Read Interrupt/Status Register

1.Check if the slave’s TX

register is empty (TXDE=1)

2.If TXDE=0

repeat step 1 else continue

3.Write the X memory address

to the slave’s TX register

+ X Memory Read Interrupt

(

—

H

–

S=0,

—

H

–

A=1, A5-A2=0011) HMRC=1 in ICS

X Memory Read Interrupt Pend

Start Interrupt Processing

1.Write contents of Host HRX

HMRC Polling Register to AGU Register:

MOVEP X:HRX,Rn

1.Check if HMRC=0 in slave’s 2.Read contents of X Memory

ICS register Address to Host HTXC reg:

2.If HMRC=1 then repeat 1 MOVEP X:(Rn),X:HTXC

else read RX register 3.HTX -

→

RX and HMRC=0

Figure 7-23. X Memory Read Procedure