Motorola DSP96002 User Manual

Page 146

8 - 6

DSP96002 USER’S MANUAL

MOTOROLA

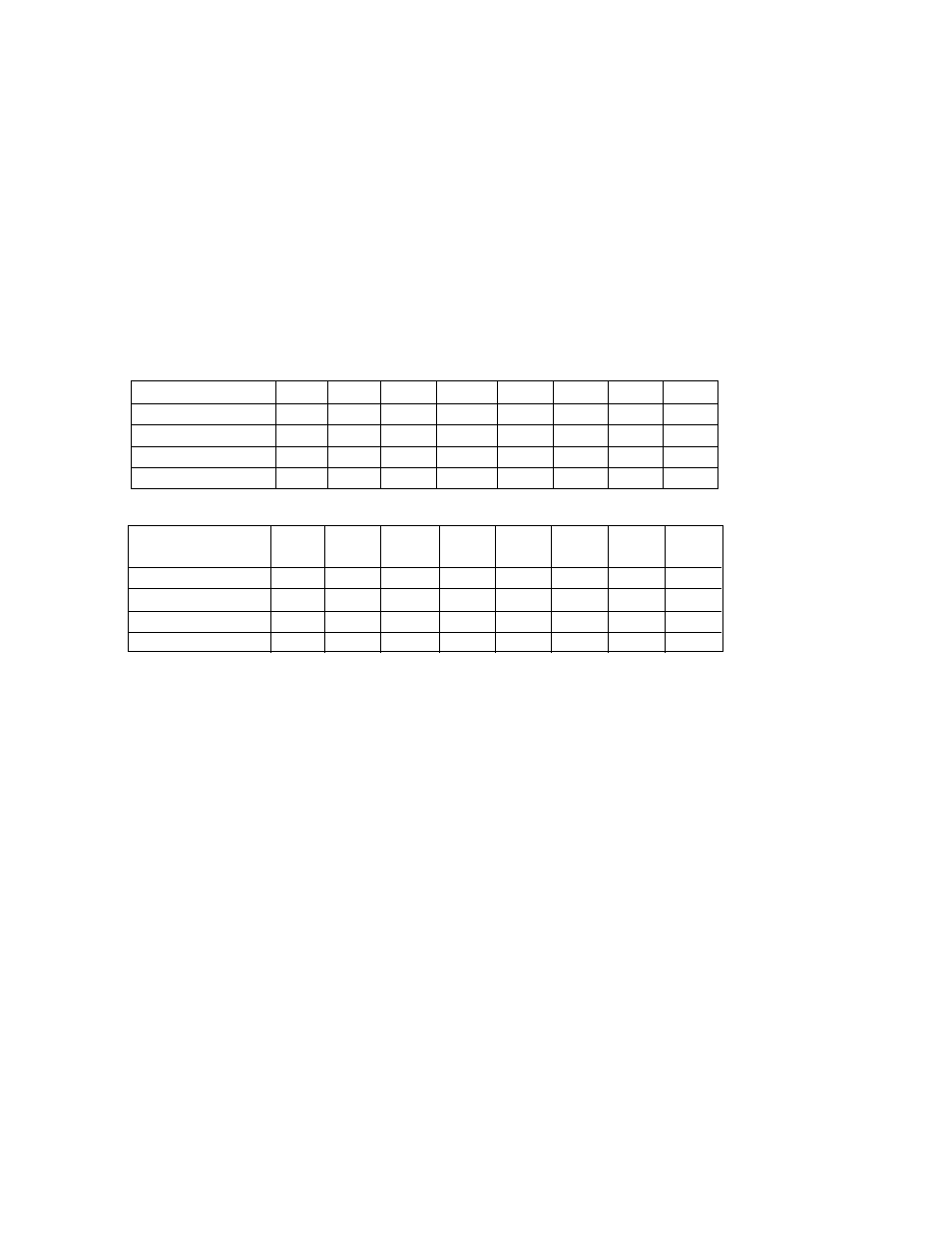

Int ctl cyc1 i

Int ctl cyc2 i

Fetch n3 n4 ii1 ii2 sr1 sr2 sr3 sr4

Decode n2 n3 n4 JSRf NOP sr1 sr2 sr3

Execute n1 n2 n3 n4 JSRf NOP sr1 sr2

*

Int ctl cyc1 i

Int ctl cyc2 i

Fetch sr5 n5 ii3 ii4 n6 n7 n8 n9

Decode RTI NOP n5 ii3 ii4 n6 n7 n8

Execute sr3 RTI NOP n5 ii3 ii4 n6 n7

i = interrupt

ii = interrupt instruction word

JSRf = fast JSR (one-word JSR instruction)

n = normal instruction word

sr = service routine word

* subsequent interrupts are enabled at this time

2. The status register is modified as follows: the interrupt mask bits I1, I0 in the MR are up-

dated to mask interrupts of the same or lower priority (except that illegal instruction, stack

error and (F)TRAPcc can always interrupt).

3. The PC will be altered by the JSR instruction so that instruction execution will continue

with the instructions located in the address pointed to by the JSR instruction.

2.

Long interrupt routines are interruptible by higher priority interrupts. The first instruction word

of the next interrupt service may reach the decoder only after the decoding of at least four in-

structions following the decoding of the first instruction of the previous interrupt.

3.

The long interrupt routine should be terminated by an RTI, which pulls the PC and SR from

the stack.

Figure 8-4. Long Interrupt Pipeline Action

Figure 8-4 illustrates the effect of a long interrupt routine on the instruction pipeline. A fast JSR (that is, a

one-word JSR instruction) is used to form the long interrupt routine. For this example, word 4 of the long

interrupt routine is an RTI. A subsequent interrupt is shown to illustrate the uninterruptable nature of the

early instructions in the long interrupt routine.

See Figure 8-5 for an example of interrupt service when the instruction that receives the internal interrupt

service request is the REP instruction (n3 in Figure 8-5). During the repeated executions of the instruction

that follows the REP instruction (n4), instruction fetches are suspended. The fetches will be reactivated

only after the loop counter is decremented to one. During the execution of n4, interrupts will not be ser-

viced. When LC finally reaches one, the fetches are reinitiated and the interrupt can be serviced. In Figure

8-5 it can be seen that n5 (loaded into the instruction latch from the backup instruction latch) is decoded

and executed as well as n6 before the first interrupt vector.