Motorola DSP96002 User Manual

Page 112

7 - 26

DSP96002 USER’S MANUAL

MOTOROLA

In DMA Mode (DMAE=1), TREQ must be set or cleared by software to select the direction of DMA transfers.

Setting TREQ defines the direction of DMA transfer to be from external DMA

→

96002, and enables the

—

H

–

R pin to request these data transfers.

See Figure 7-15 and Figure 7-16 for a summary of the effect of TREQ on the

—

H

–

R pin. TREQ is cleared

by HW/SW reset.

7.4.13.6

ICS Transmitter Ready Request Enable (TYEQ) Bit 5

TYEQ is used to enable interrupts via the Host Request

—

H

–

R pin when the Transmitter Ready (TRDY)

status bit is set. When TYEQ is cleared, TRDY interrupts are disabled. When TYEQ is set, the Host Request

—

H

–

R pin will be asserted if TRDY is set.

See Figure 7-15 for a summary of the effect of TYEQ on the

—

H

–

R pin. TYEQ is cleared by HW/SW reset.

In DMA Mode (DMAE=1), TYEQ must be cleared.

7.4.13.7

ICS Initialize (INIT) Bit 6

The INIT bit is used by the host processor to force initialization of the HI hardware. This may or may not be

necessary, depending on the software design of the interface.

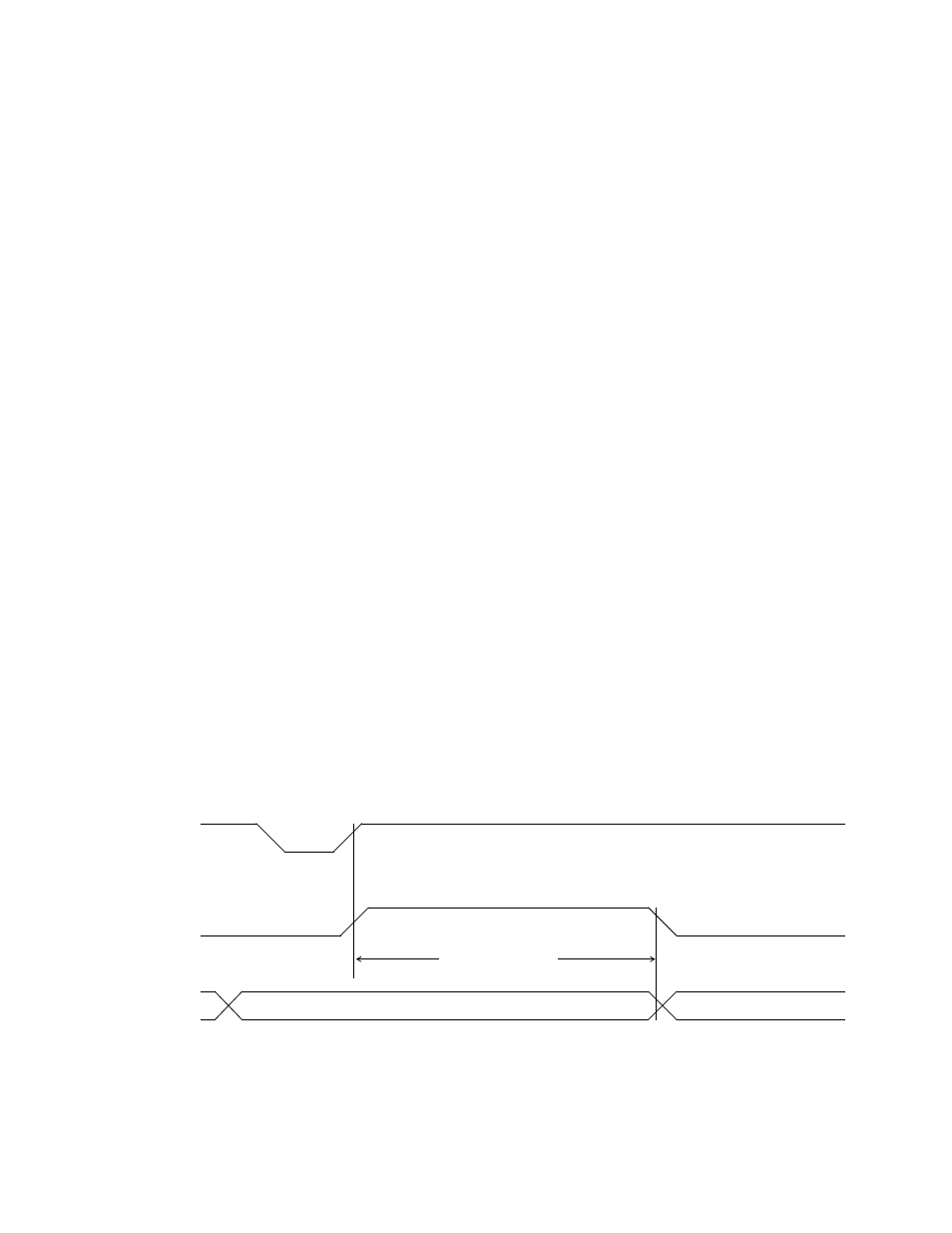

To correctly initialize the HI, set the INIT bit with the other control bits in ICS which determine the initialization

procedure (TREQ, RREQ). All bits may be written in the same command. After setting the INIT bit, the HI

starts the initialize procedure, and at the end of the procedure, the HI clears the INIT bit. During the initialize

procedure, the host processor should not attempt to read RX, write TX or write the ICS register. The host

processor should first ensure that the Initialize procedure has completed, using one of the following tech-

niques:

1.

When using the

—

H

–

R pin for handshake, wait until

—

H

–

R is asserted and then start writing/

reading data.

—

T

–

S

INIT bit

in ICS

RX, TX

no accesses

first access

3T

c

+Th minimum

write ICS

INIT=1

Figure 7-14. Minimum Delay to Ensure Correct INIT Execution