Motorola DSP96002 User Manual

Page 100

7 - 14

DSP96002 USER’S MANUAL

MOTOROLA

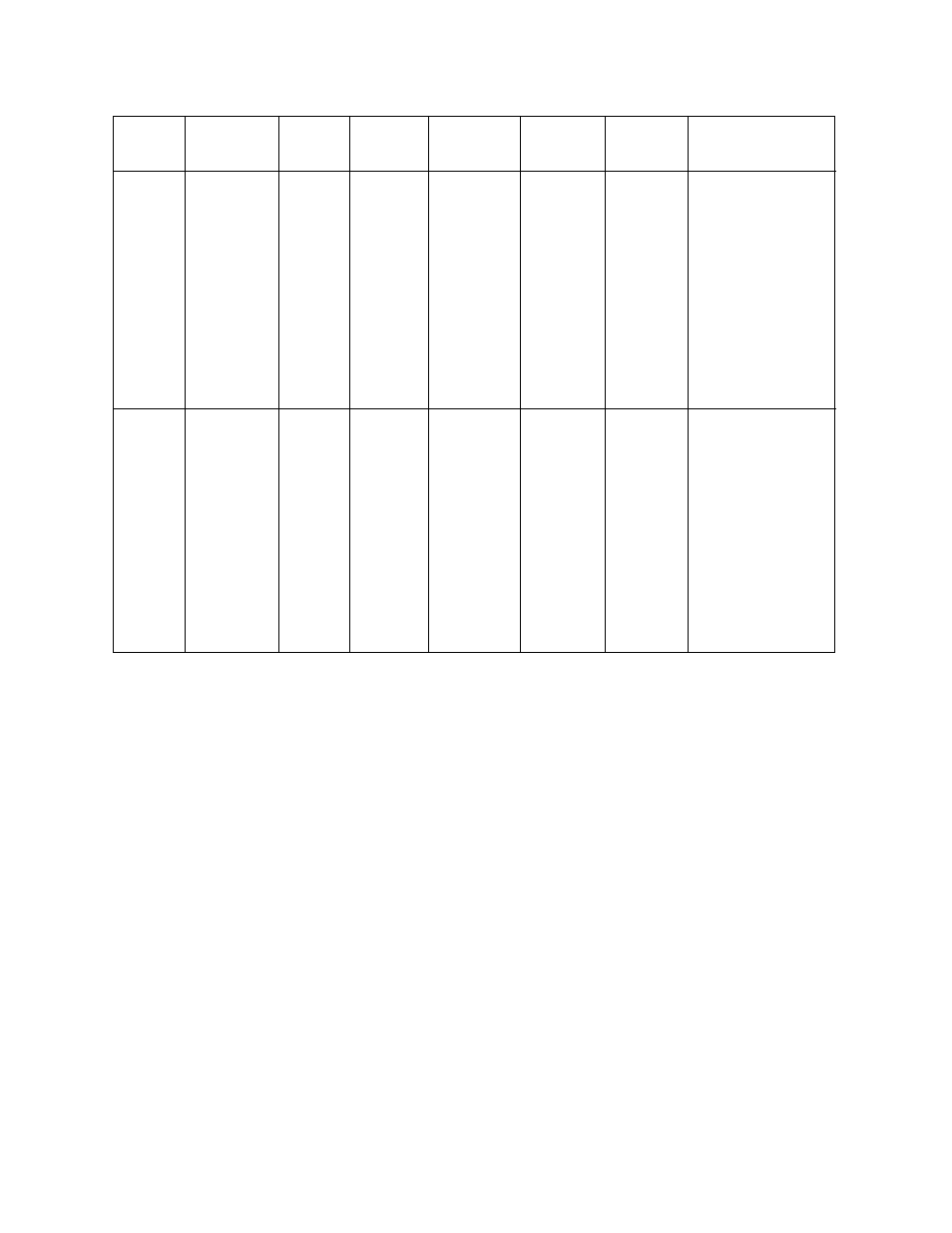

7.4.4 HI Programming Model

The HI block diagram is shown in Figure 7-9. The HI has two programming models - one for the DSP96002

programmer and one for the external host processor programmer. In most cases, the notation used reflects

the DSP96002 perspective. The HI - DSP96002 Programming Model is shown in Figure 7-10. The HI - Ex-

ternal Host Processor Programming Model is shown in Figure 7-11. The HI Interrupt Structure is shown in

Figure 7-13. The DSP96002 has two HIs. The registers of the two HIs are identical except for the addresses.

Their names have an A or B suffix identifying the port they are connected to.

7.4.5 Host Transmit Data Register (HTX) - DSP96002 Side

The Host Transmit register (HTX) is used for DSP96002 to host processor data transfers. The HTX register

is viewed as a 32-bit write-only register by the DSP96002. Writing the HTX register clears HTDE. The

DSP96002 may program the HTIE bit to cause a Host Transmit Data interrupt when HTDE is set. The HTX

register is transferred as 32-bit data to the Receive Register RX if both the HTDE bit and the Receive Data

Full RXDF status bit are cleared. This transfer operation sets RXDF and HTDE.

Register

Register

HW/SW

HOST

INIT

INIT

INIT

Comments

Name

Contents Reset

Reset

TREQ=1

TREQ=0

TREQ=1

RREQ=0

RREQ=1

RREQ=1

HCR

HYWE

0 - - - -

HYRE

0 - - - -

HXWE

0 - - - -

HXRE

0 - - - -

HPWE

0 - - - -

HPRE

0 - - - -

HRES

1 1 - - -

HF3-HF2

0 - - - -

HCIE

0 - - - -

HTIE

0 - - - -

HRIE

0 - - - -

HSR

HYWP

0 0 0 - 0

HYRP

0 0 0 - 0

HXWP

0 0 0 - 0

HXRP

0 0 0 - 0

HPWP

0 0 0 - 0

HPRP

0 0 0 - 0

HDMA

0 - - - -

HF1-HF0

0 - - - -

HCP

0 - - - -

HTDE

1 1 - 1 1

HRDF

0 0 0 - 0

Figure 7-8. Host Interface Reset - DSP96002 Side