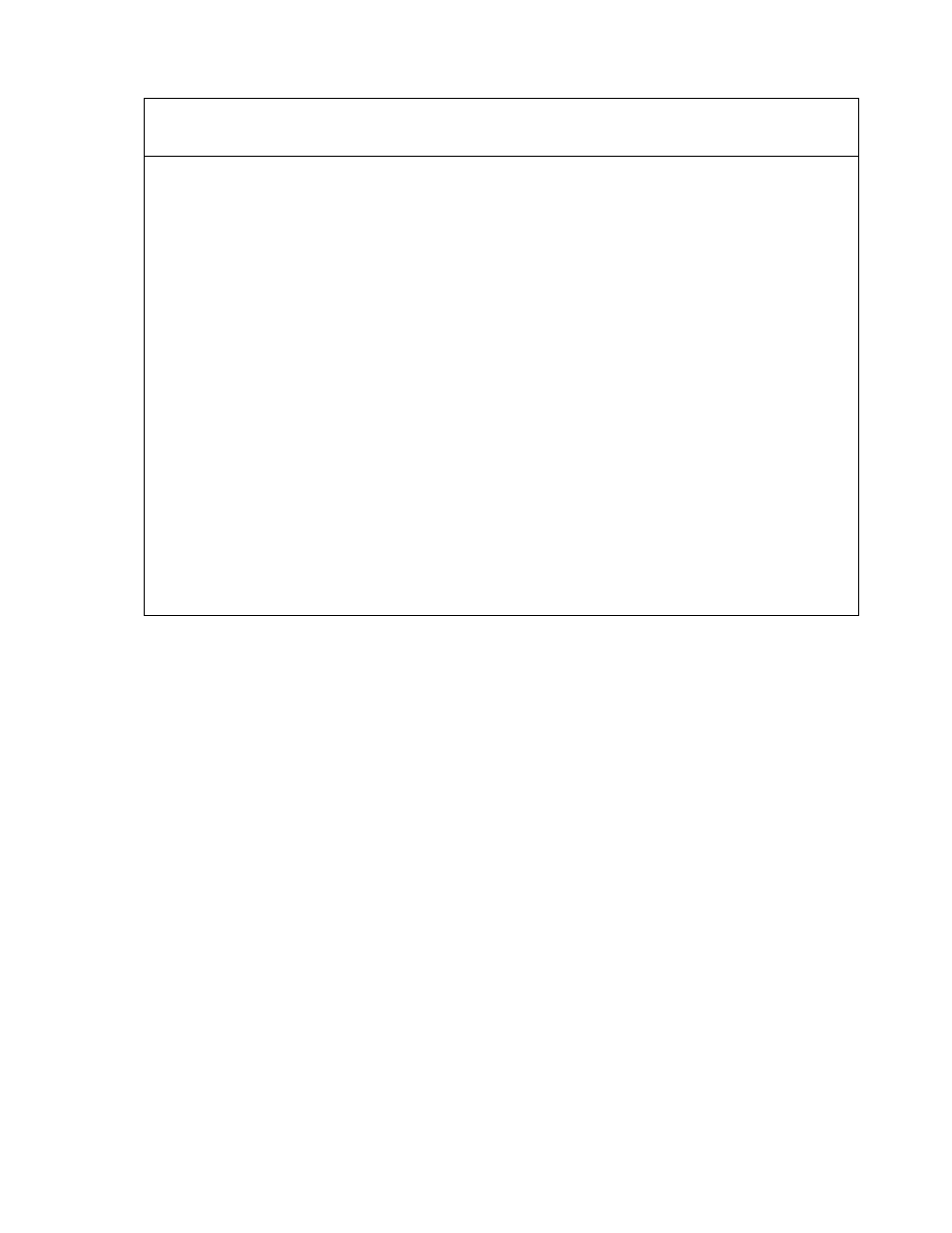

Figure a-1. addressing mode summary – Motorola DSP96002 User Manual

Page 190

A - 2

DSP96002 USER’S MANUAL

MOTOROLA

A.3

CONDITION CODE COMPUTATION

The CCR contains the condition code bits Carry (C), Overflow (V), Zero (Z), Negative (N), Infinity (I), Local

Reject (LR), Reject (

–

R), and Accept (A).

The C, V, Z, N, I, LR,

–

R, and A bits are true condition code bits that reflect the condition of the result of a

Data ALU operation. The C, V, Z and N bits are also affected by Address Generation Unit calculations

during MOVETA instruction execution. The CCR bits are not affected by data transfers over the X, Y or

global data buses.

The

standard definition

of the CCR bits is given below. Exceptions to these are given in Figure A-4.

C(Carry)

Set if a carry is generated in an integer addition. Also set if a borrow is generated in an

integer subtraction. The carry or borrow is generated out of the most significant bit

(MSB) of the result. The carry bit is also modified by bit manipulation, rotate, and shift

integer instructions as well as by the Address Generation Unit operation when execut-

ing MOVETA instructions. Cleared otherwise. The carry bit is not affected by floating-

point instructions. The C bit is cleared during processor reset.

V(Overflow)

Set if an arithmetic overflow occurs in a fixed point operation. This indicates that the

result is not representable in the destination size. The V bit is not affected by floating-

point operations unless they have a fixed point result. The overflow bit is also modified

Register Direct

Data or Control Register

–

–

X

Note 1

Address Register

–

–

X

Rn

Address Offset Register

–

–

X

Nn

Address Modifier Register

–

–

X

Mn

Address Register Indirect

No Update

100

Rn

X

X

X

X

(Rn)

Postincrement by 1

011

Rn

X

X

X

X

(Rn)+

Postdecrement by 1

010

Rn

X

X

X

X

(Rn)-

Postincrement by Offset Nn

001

Rn

X

X

X

X

(Rn)+Nn

Postdecrement by Offset Nn

000

Rn

X

X

X

(Rn)- Nn

Indexed by Offset Nn

101

Rn

X

X

(Rn+Nn)

Predecrement by 1

111

Rn

X

X

-(Rn)

Long Displacement

–

Rn

X

(Rn+displacement)

PC Relative

Long Displacement

–

–

(PC+displacement)

Short Displacement

–

–

(PC+xx)

Address Register

–

Rn

(PC+Rn)

Special

Immediate Data

110

100

X

#Data

Absolute Address

110

000

X

X

label

Absolute Short Address

–

–

X

aa

I/O Short Address

–

–

X

pp

Immediate Short Data

–

–

#xx

Short Jump Address

–

–

X

xx

Implicit

–

–

X

Note 1: Refer to Figure A-6 for the assembler syntax.

Figure A-1. Addressing Mode Summary

Addressing

Mode

Reg

Categories

Assembler

Addressing

Mode

U

P

M

A

Syntax