Motorola DSP96002 User Manual

Page 775

MOTOROLA

DSP96002 USER’S MANUAL

D-23

D.1.5.2

Multiply unit

The multiply unit consists of a hardware multiplier, an exponent adder, and a control unit, as shown in Figure

D-11. The multiply unit accepts two 44 bit input operands for floating point multiplications, each consisting

of a sign bit, eleven exponent bits, the explicit integer bit, and 31 fractional bits. Note that for full double pre-

cision operands, as obtained by double precision MOVEs, the least significant 8 bits of the fraction are sim-

ply truncated. Multiply operations occur in parallel with and independent of data moves over the X and Y

data buses.

The hardware multiplier accepts the two 32-bit mantissas (integer bit + 31 bit fraction), and delivers a 64 bit

result, as shown in Figure D-12. This result is automatically rounded to a 32-bit mantissa for SEP arithmetic

or a 24 bit mantissa for SP arithmetic, as specified by the instruction opcode. The result is stored into the

mantissa portion of the destination register.

The exponent adder takes the two unsigned (i. e., biased) operand exponents, adds them together, and

subtracts the bias, resulting in an 11-bit biased exponent which is stored in the exponent part of the floating

point format in the destination register, as depicted in Figure D-13.

D.1.5.3

Adder/Subtracter Unit

The adder unit is depicted in Figure D-14, and consists of a barrel shifter and normalization unit, an add unit,

a subtract unit, an exponent comparator and update unit and a special function unit. The adder/subtracter

unit accepts 44-bit floating point operands, and delivers 44-bit results. The adder/subtracter operations de-

liver the sum and the difference of the same two floating point operands in a single instruction cycle. In ad-

dition, the barrel shifter used for mantissa alignment in floating point additions and subtractions is used for

executing multibit shifts. The adder/subtracter operates in parallel with and independent of data moves over

the X and Y data buses.

The add unit is a high speed 32-bit adder, used in all floating-point non-multiply operations. For floating point

operations, 32-bit mantissas (1 integer bit and 31 fractional bits) are first "aligned" for floating point addition

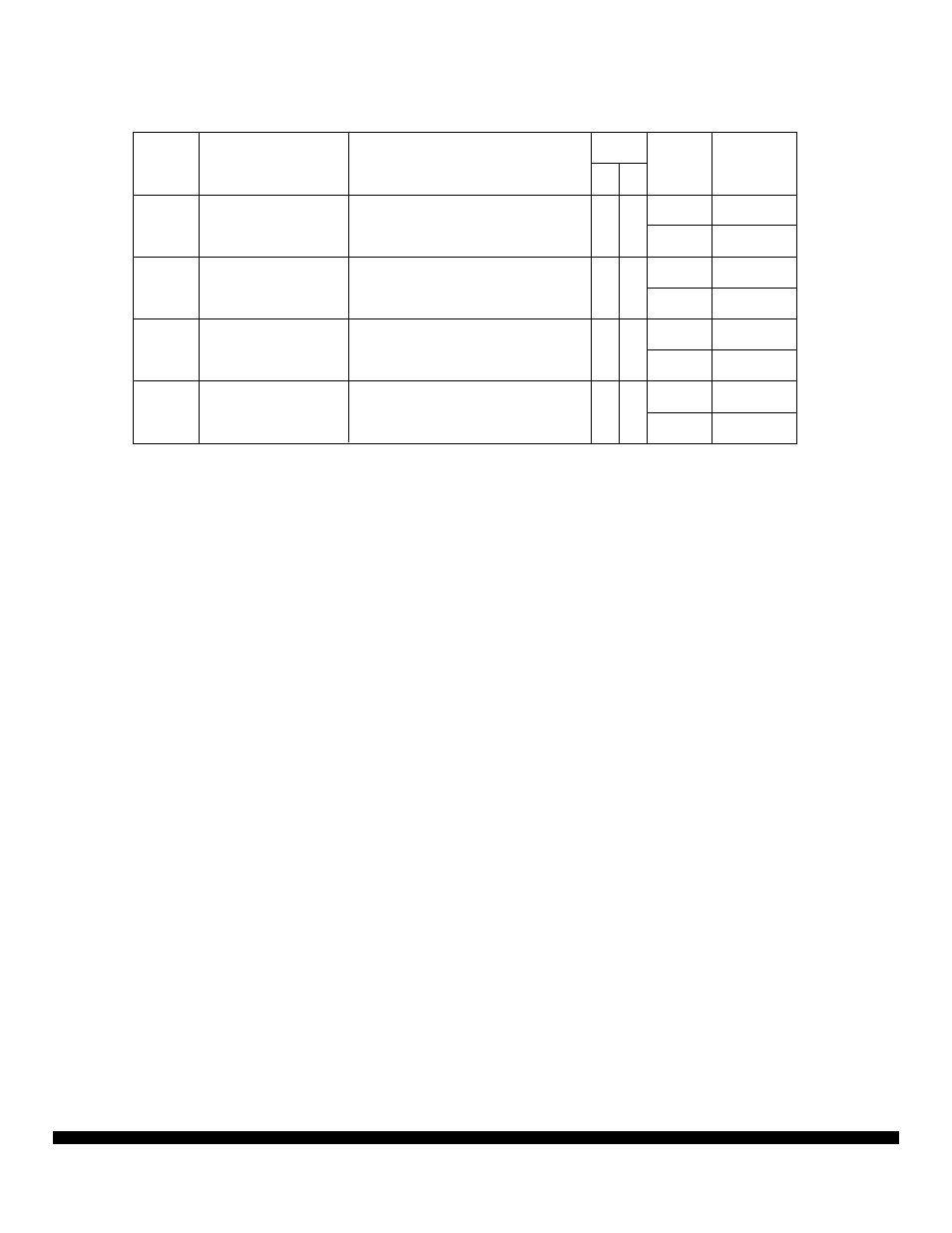

ROUND EXPONENT RANGE DATA ALU OPERATION TAGS MOVE MOVE OUT

TO BEFORE ROUND RESULT OUT RESULT

(UNBIASED) U V TYPE

SEP -150< e < -126 denormalized in SP 0 0 SP WRONG

normalized in SEP

DP CORRECT

SEP -1023< e < -149 zero in SP 0 0 SP WRONG

normalized in SEP

DP CORRECT

SEP -1054< e< -1022 zero in SP 0 1 SP WRONG

denormalized in SEP

DP CORRECT

SEP e< -1053 zero in SP 0 0 SP CORRECT

zero in SEP (underflow)

DP CORRECT

Figure C- 4. Data ALU Results/Move Compatibility Summary