Motorola DSP96002 User Manual

Page 153

MOTOROLA

DSP96002 USER’S MANUAL

8 - 13

8.5.2.5 IRQB Trigger Mode - IBL2 (Bit 6)

The IRQB Trigger Mode (IBL2) bit specifies the trigger method for the external interrupt input IRQB.

8.5.2.6 IRQB Status - IRBS (Bit 7)

The read-only IRQB Status (IRBS) bit indicates the status of the interrupt request for the external interrupt

input IRQB. If the IRQB interrupt is defined as edge-sensitive and it is enabled, the IRBS bit indicates the

state of the edge-detection latch. If the IRQB interrupt is defined as level-sensitive or is disabled, the

IRBS bit indicates the state of the IRQB pin after internal synchronization.

8.5.2.7

IRQC Interrupt Priority Level - ICL1-ICL0 (Bits 8-9)

The IRQC Interrupt Priority Level (ICL1-ICL0) bits are used to enable and specify the priority level of the

external interrupt input IRQC.

8.5.2.8 IRQC Trigger Mode - ICL2 (Bit 10)

The IRQC Trigger Mode (ICL2) bit specifies the trigger method for the external interrupt input IRQC.

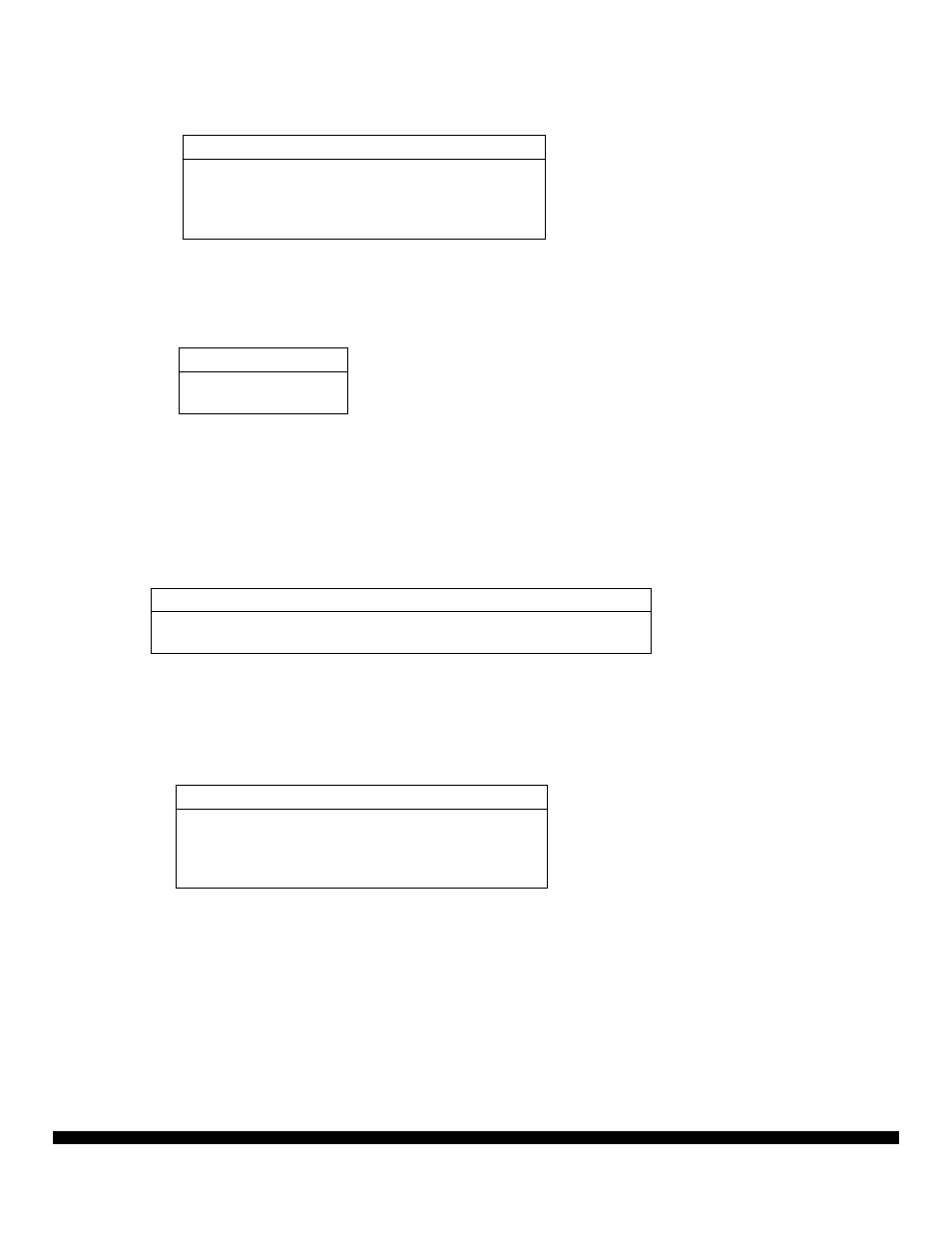

IBL1 IBL0 Enabled Int. Priority Level (IPL)

0

0

no

-

0

1

yes

0

1

0

yes

1

1

1

yes

2

IBL2 Trigger Mode

0

level

1

negative edge

IRBS Status (edge and enabled) IRQB pin (level or disabled)

0

Serviced

High

1

Pending

Low

ICL1 ICL0 Enabled Int. Priority Level (IPL)

0

0

no

-

0

1

yes

0

1

0

yes

1

1

1

yes

2