Motorola DSP96002 User Manual

Page 820

38

MOTOROLA

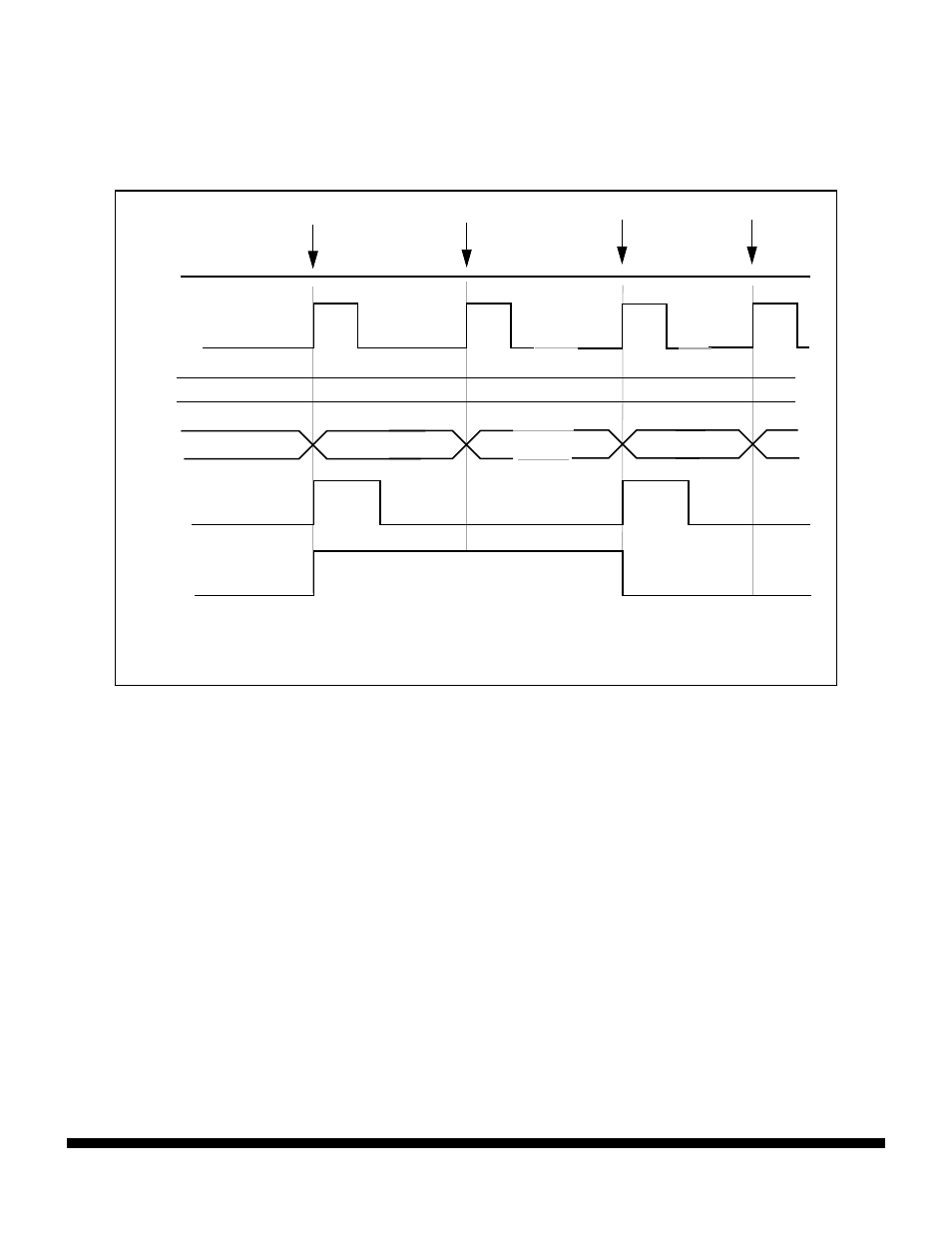

TS bit in TCSR is set and, if the TIE is set, an interrupt is generated.The counter is reload-

ed with the value contained by the TCR and the entire process is repeated until the timer

is disabled (TE=0). Each time the counter reaches 0, the TIO output pin will be toggled.

The INV bit determines the polarity of the TIO output. Figure 13 illustrates Timer Mode 2.

6.4.4

Timer Mode 4 (Pulse Width Measurement Mode)

Timer Mode 4 is defined by TC2-TC0 equal to 100.

In this mode, TIO acts as a gating signal for the DSP’s internal clock. With the timer en-

abled (TE=1), the counter is driven by a clock derived from the DSP’s internal clock

divided by two (CLK/2). The counter is loaded with 0 by the first transition occurring on the

TIO input pin and starts incrementing. When the first edge of opposite polarity occurs on

TIO, the counter stops, the TS bit in TCSR is set and, if TIE is set, an interrupt is gener-

ated. The contents of the counter is loaded into the TCR. The user’s program can read

the TCR, which now represents the widths of the TIO pulse. The process is repeated until

the timer is disabled (TE=0).The INV bit determines whether the counting is enabled when

TIO is high (INV=0) or when TIO is low (INV=1). Figure 14 illustrates Timer Mode 4 when

INV=0 and Figure 15 illustrates Timer Mode 4 with INV=1.

TE

TCR

last event

N

Counter

N

0

N

Interrupt

first event

last event

N-1

TIO

new event

N-1

0

Clock

Figure 13 - Standard Timer Mode, Internal Clock, Output Toggle Enable

(CLK/2)