Motorola DSP96002 User Manual

Page 17

2 - 14

DSP96002 USER’S MANUAL

MOTOROLA

3. 6.1.2

—

W

–

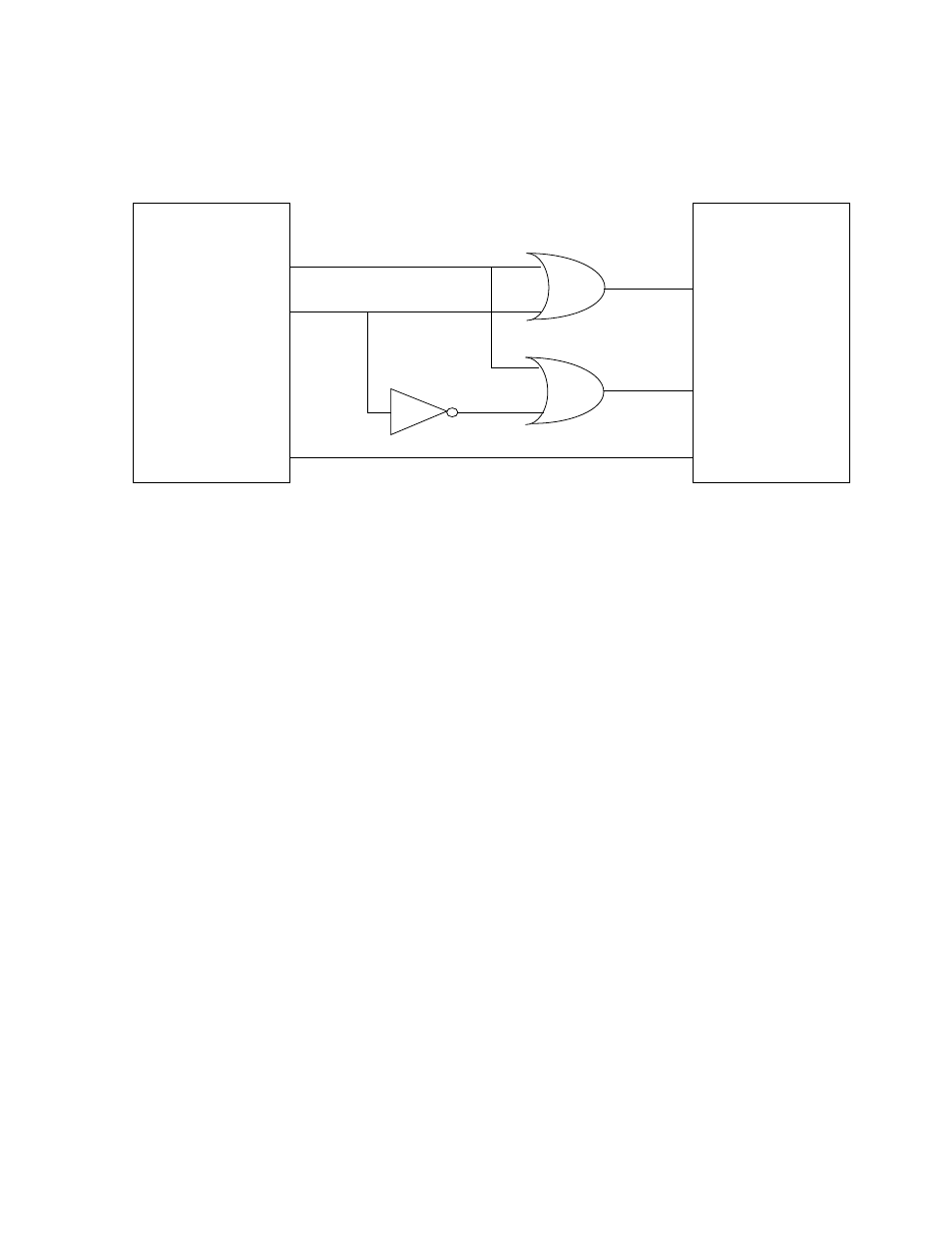

E Controlled Writes

This form of static interface uses the memory write enable (

—

W

–

E) as the write strobe. The DSP96002

R/

—

W signal is used to form a late read/write indication by gating it with

—

T

–

S. This form is the one used

by the 56000/1 bus interface. Proper data buffer enable control requires a separate output enable (

—

O

–

E) input on the memory to avoid multiple data buffers colliding on the data bus. The interface schematic

is shown in Figure 2-6.

The advantage of this technique is that access time is measured from S1, S0 or addresses instead of

—

T

–

S. Hence slower memories can be used. The disadvantage of this technique is that the write data hold

will be shortened because the

—

W

–

E signal is delayed by the OR gate.

3.6.2 Dynamic RAM and Video RAM Support

Modern dynamic memory (DRAM) and video memory (VRAM) are becoming the preferred choice for a

wide variety of computing systems based on

4:7.

Cost per bit due to dynamic storage cell density.

4:8.

Packaging density due to multiplexed address and control pins.

4:9.

Improved performance relative to static RAMs due to fast access modes (page, static col-

umn, nibble and serial shift (VRAM)).

4:10. Commodity pricing due to high volume production.

DSP96002

—

R/

—

STATIC RAM

—

—

O

–

—

C

–

S1 or S0

Figure 2-6.

—

W

–

E Controlled Writes Interface To Static RAM

The disadvantage of this technique is that access time is measured from

—

T

–

S instead of from the address

or

—

B

–

S. Hence faster memories are required.