Motorola DSP96002 User Manual

Page 514

A - 326

DSP96002 USER’S MANUAL

MOTOROLA

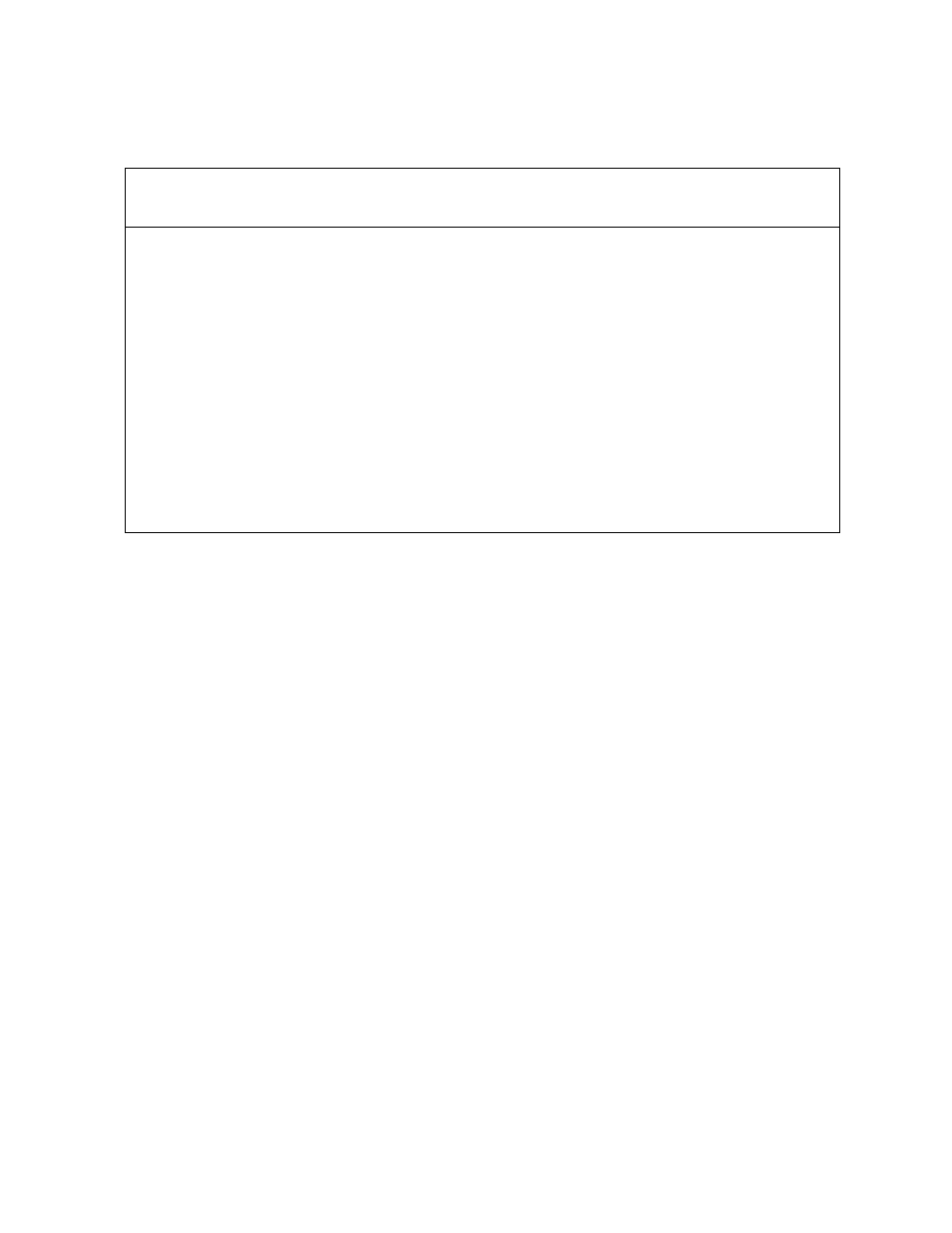

A.9.13 Memory Access Timing Summary

Access

X Mem

Y Mem

P Mem

I/O

+ ax

+ ay

+ ap

+ aio

+ axy

Type Access

Access

Access

Access

Cycle

Cycle

Cycle

Cycle

Cycle

X:

Int

––

––

––

0

––

––

––

––

X:

Ext

––

––

––

wx

––

––

––

––

Y:

––

Int

––

––

––

0

––

––

––

Y:

––

Ext

––

––

––

wy

––

––

––

P:

––

––

Int

––

––

––

0

––

––

P:

––

––

Ext

––

––

––

wp

––

––

IO:

––

––

––

Int

––

––

––

0

––

IO:

––

––

––

Ext

––

––

––

wio

––

L: XY:

Int

Int

––

––

––

––

––

––

0

L: XY:

Int

Ext

––

––

––

––

––

––

wy

L: XY:

Ext

Int

––

––

––

––

––

––

wx

L: XY:

Ext

Ext

––

––

––

––

––

––

2+wx+wy

where

wx

= external X memory access wait states

wy

= external Y memory access wait states

wp

= external P memory access wait states

wio = external I/O memory access wait states

Figure A-20 Memory Access Timing Summary

A.10 INSTRUCTION SEQUENCE RESTRICTIONS

Due to the pipelined nature of the DSP core processor, there are certain instruction sequences that are

forbidden and will cause undefined operation. Most of these restricted sequences would cause contention

for an internal resource, such as the Stack Register.

The DSP assembler will flag these sequences as an assembly error. These restrictions are listed below.

A.10.1 Restrictions Near the End of DO Loops

Proper loop operation is guaranteed if no instruction starting at address LA-2, LA-1 or LA specifies the pro-

gram controller registers SR, SP, SSL, LA, LC or (implicitly) PC as a destination register; or specifies SSH

as a source or destination register.