Figure 2-4. bus status encoding – Motorola DSP96002 User Manual

Page 11

2 - 8

DSP96002 USER’S MANUAL

MOTOROLA

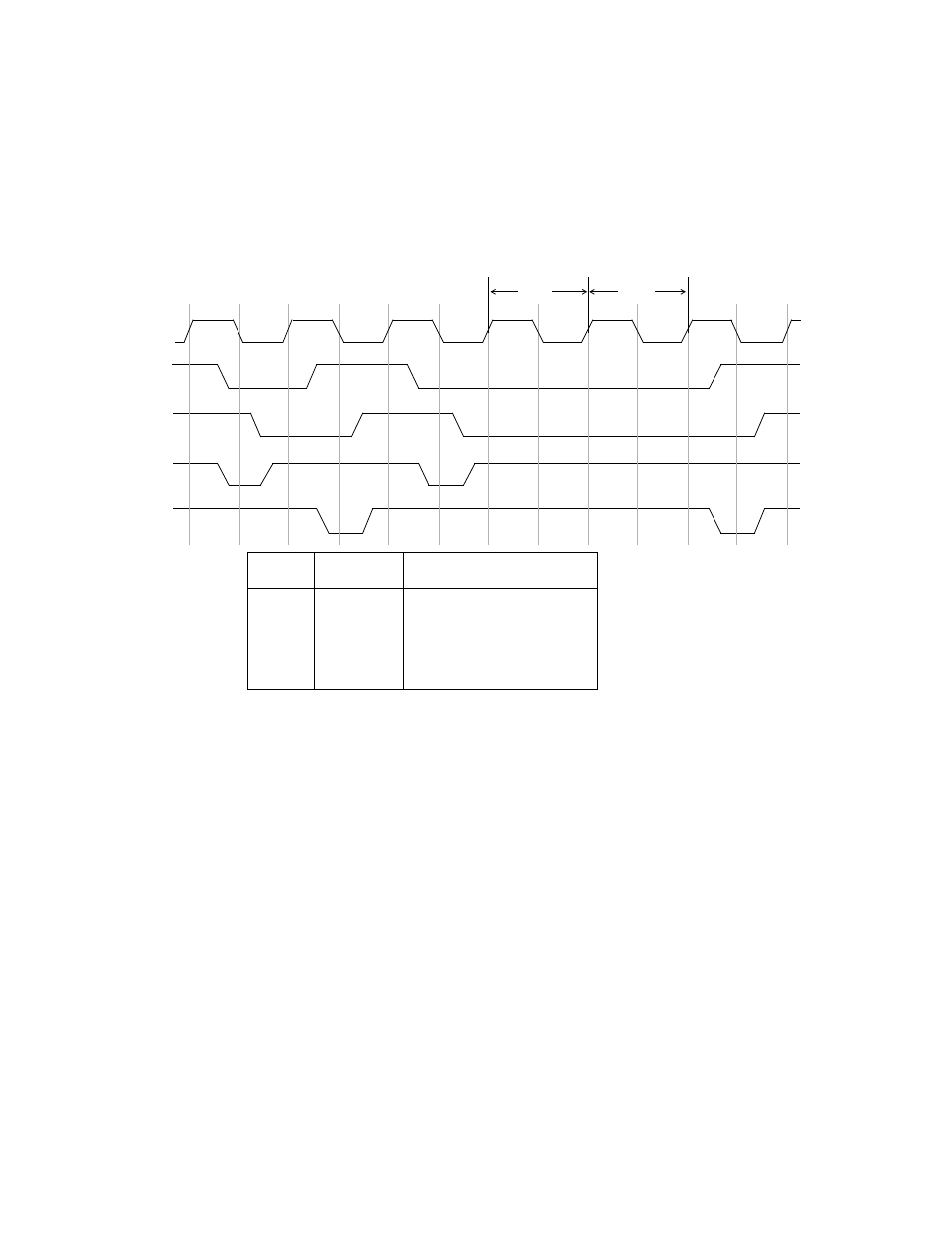

When a bus master, the combination of

—

B

–

S and

—

T

–

S can be decoded externally to

determine the status of the current bus cycle and to generate hardware strobes useful

for latching address and data signals. The encoding is shown in Figure 2-4.

—

T

–

A

(Transfer Acknowledge) - active low input. If the DSP96002 is the bus master and either

there is no external bus activity or the DSP96002 is not the bus master, the

—

T

––

A input

is ignored by the core. The

—

T

–

A input is a synchronous "DTACK" function which can

extend an external bus cycle indefinitely.

—

T

–

A must be asserted and deasserted syn-

chronous to the input clock (CLK) for proper operation.

—

T

–

A is sampled on the falling

edge of the input clock (CLK). Any number of wait states (0, 1, 2, ..., infinity) may be

inserted by keeping

—

T

–

A deasserted. In typical operation,

—

T

–

A is deasserted at the

start of a bus cycle, is asserted to enable completion of the bus cycle and is deasserted

before the next bus cycle. The current bus cycle completes one clock period after

—

T

–

A is asserted synchronous to CLK. The number of wait states is determined by the

—

T

–

A input or by the Bus Control Register (BCR), whichever is longer. The BCR can be

used to set the minimum number of wait states in external bus cycles. If

—

T

–

A is tied

low (asserted) and no wait states are specified in the BCR register, zero wait states will

be inserted into external bus cycles.

Figure 2-4. Bus Status Encoding

—

B

–

S

—

T

–

S Bus Status

Strobe Generation Application

1

1

Idle

0

1

Cycle Start

Address Strobe (

—

A

–

S)

0

0

Wait

1

0

Cycle End

Data Strobe (

—

D

–

S)

t0

t1

t2

t3

t0

t1

t2

tw

t2

tw

t2

t3

CLK

—

B

–

—

T

–

S

—

D

–

—

A

–

WS

WS